Chapter 1 - Overview of the QED Hardware

This manual describes the hardware of the QED Board and QED Product Design Kit and presents sample QED-Forth programs that make it easy to use the hardware features. It is strongly recommended that you read the booklet titled "Getting Started with the QED Board" and this introductory chapter before proceeding to read the rest of this manual.

Other Hardware Documentation

The QED Board is based on a new version of the 68HC11 microcontroller, called the 68HC11F1. Included with this documentation package are two books published by Motorola that describe the chip. The thick book titled HC11 -- M68HC11 Reference Manual will be referred to as HC11. It thoroughly describes how to use microcontrollers of the 68HC11 variety, but it does not describe some of the enhanced features that appear in the F1 version. The thin reference book titled HC11F1-- MC68HC11F1 Technical Data provides details on the new version of the 68HC11 CPU installed on your QED Board; it will be referred to as F1 .

This hardware manual presents concise summaries of the microcontroller's hardware features along with commented example programs that facilitate access to the QED Board's hardware. Details that have been left out can be found in the Motorola books, and page number references to F1 and HC11 are provided as frequently as possible.

Getting Started

The QED Board is very easy to use. You can start programming immediately after plugging in the board and connecting it to the RS232 serial line of your personal computer or terminal. You type your source code (that is, your QED-Forth commands and definitions) from the terminal, or better yet, edit your source code into a file and use the terminal to transfer the file to the QED Board. The terminal should be configured as follows:

- 9600 baud

- 8 data bits

- No parity

- 1 start bit

- 1 stop bit

- XON/XOFF handshaking enabled

- Wait for linefeed before sending next line

Your terminal program must wait at the end of each line for a linefeed character before sending the next line. Depending on the terminal program, the linefeed character can be denoted as LF, ˆJ, ascii decimal 10, or ascii hex A. Most terminals allow you to specify a "prompt character" (in this case a linefeed) that must be received before sending each line. These options are typically associated with the "file transfer" or "text transfer" menu of your terminal program. In addition, XON/XOFF protocol should be enabled if it is available; this ensures smooth reception of data dumps from the QED Board.

Please read the booklet titled "Getting Started With the QED Board". It gives step-by-step instructions that describe how to set up and start programming your QED Board or Product Design Kit.

QED Board Hardware Overview

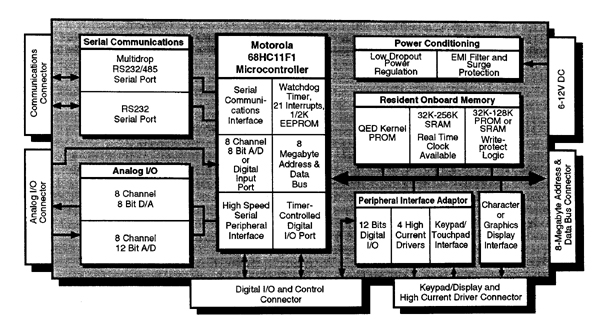

To put the capabilities of the QED Board in perspective, we will review the key hardware systems as shown in the block diagram in Figure 1.1.

Figure 1.1. Block diagram of the QED Board.

The 68HC11 Integrates a Variety of I/O and Control Functions

The central block in Figure 1.1 represents the 68HC11F1 microcontroller. This chip integrates a central processing unit (CPU), communications, analog and digital I/O, timing capabilities, and memory. It provides the core capabilities of the QED Board. In this document we will refer to the microcontroller chip as the 68HC11F1, or the 68HC11, or simply the HC11. This section provides a brief description of the many functions integrated on the 68HC11 chip.

The processor includes an 8 bit timer-controlled digital I/O port called PORTA. The timer functions include "input captures" that facilitate accurate measurement of pulse widths, "output compares" that make it easy to generate pulse trains and pulse-width modulated waveforms, and a pulse accumulator. These functions are backed up by interrupts that simplify real-time response to external events.

An 8 channel input port (called PORTE) on the processor can be configured to read either analog or digital inputs. Analog inputs are converted to an 8 bit digital number by a built-in analog to digital (A/D) converter.

The 68HC11 includes a built-in serial communications interface (SCI). The SCI is an asynchronous interface, meaning that there is no clock transmitted with the data. Using the SCI, an 8 MHz QED Board can transmit and receive data at standard baud rates to 9600 baud, and at non-standard rates as high as 125 Kbaud; these maximum baud rates double if the board is clocked at 16 MHz. Onboard serial interface chips generate the logic levels necessary to implement either the RS232 or RS485 protocol using the SCI.

The QED Board implements an optional second serial channel using two of the timer-controlled PORTA pins supported by pre-coded software in the QED-Forth kernel. Onboard serial interface chips generate the logic levels necessary to implement the RS232 protocol for the secondary serial port. Data rates up to 2400 baud can be sustained by the secondary serial port if the board is clocked at 8 MHz; the maximum rate doubles to 4800 baud if the board is clocked at 16 MHz.

Four bits of PORTD on the 68HC11 can be configured either as general purpose digital I/O or as a high speed serial peripheral interface (SPI). The SPI is capable of data transfer rates up to 1 megabit per second if the QED Board is clocked at 8 MHz, and up to 2 megabits per second if the board is clocked at 16 MHz. Many useful devices communicate via such a synchronous (clocked) serial interface. Multiple peripheral devices can communicate on this interface as long as each device has a unique chip select signal. As explained below, two optional onboard analog devices exchange data with the 68HC11 via the SPI.

The 68HC11 chip integrates several other features. A watchdog timer can be configured to reset the processor if the application program fails to execute properly. A clock monitor is available to reset the processor if the clock fails. External interrupt request pins and a variety of interrupt functions facilitate quick responses to real-time events.

512 bytes of electrically erasable PROM (EEPROM) are on the 68HC11 chip. QED-Forth uses 192 bytes of this nonvolatile memory to implement the SAVE/RESTORE functions and to revector interrupt calls; the remaining 320 bytes are available for your application. EEPROM provides a convenient way to store calibration constants and other information that must be periodically updated.

The 68HC11 communicates with external memory via a 16 bit address bus and an 8 bit data bus. Its native address space is 64 Kilobytes (equal to 65,536 bytes, and often written as 64K). The QED Board expands the addressable memory space to 8 Megabytes by effectively adding 8 "page" bits to the address bus. The memory architecture is optimized for fast execution, and the QED-Forth operating system makes page changing transparent to the user. Once you set up your starting memory map, QED-Forth handles all of the details of accessing memory.

Optional DAC and High Resolution A/D Converter

An optional 8 channel (or 4 channel differential) A/D with 12 bits of resolution facilitates accurate measurement of analog inputs. An optional 8 channel digital to analog converter (DAC) allows the QED Board to generate analog outputs, or to multiply an analog signal by a digitally specified gain factor (to implement volume control, for example). Both of these devices communicate with the processor via the high speed serial peripheral interface (SPI).

Resident Onboard Memory

As indicated in Figure 1.1, the QED Board has sockets for 3 standard memory devices. Each socket can accommodate up to 128K of memory. The first socket holds the QED-Forth kernel in a 64K PROM. This software provides a complete resident programming environment, multitasking executive, and libraries of mathematics and device driver routines.

The middle socket on the QED Board accommodates a 32K or 128K static RAM. Options available for this socket include a battery-backed RAM, and a battery-backed RAM with a built-in real-time clock. Built-in software routines can set and read the real-time clock.

The third socket is called the RAM/ROM socket; it can accommodate either RAM or PROM devices ranging from 32K to 128K in size. This socket has been designed to hold your application code in battery-backed RAM during program development, and to hold your final application PROM in production versions of your board.

During program development, QED-Forth compiles your code into battery-backed RAM in the RAM/ROM socket at pages 4, 5, 6, and 7. You can write-protect 64K segments of memory with the flip of a switch; this converts the RAM into "emulated PROM". You can see exactly how your application will run in a PROM without having to actually burn a PROM; this saves you a lot of time and hassle during program development. When your application is completely debugged, you can invoke built-in routines to dump out the image of your program in a standard format accepted by PROM burners. Plugging your application PROM into the RAM/ROM socket and toggling the RAM/ROM switch (DIP switch #3 on the board) to the "ROM" position completes the development process and puts you into production.

The Peripheral Interface Adapter

The Peripheral Interface Adapter (PIA) shown in Figure 1.1 adds 24 digital I/O lines to the QED Board. Eleven of these are dedicated to the keypad/display interface. Another bit of the PIA is dedicated to the creation of the chip select signal for the 12 bit A/D. An additional I/O line controls the direction of data transfer if the optional RS485 serial link is used. Eleven of the PIA's I/O lines are completely uncommitted. The allocation of I/O lines is explained further below.

Power Conditioning and Regulation

The QED Board can be powered by applying:

- a "raw" unregulated DC input voltage between 6 and 12 Volts, or

- a battery with voltage greater than 5.6 Volts, or

- a regulated +5 Volt supply.

If you power the board with an unregulated DC supply or a battery, the onboard circuitry is protected by a built-in surge protector and electromagnetic interference (EMI) suppression circuitry. This greatly improves the reliability of the electronics in harsh industrial environments. The QED Board consumes approximately 100 milliamps (mA) of current when clocked at 8 MHz.

An onboard dual voltage regulator creates two +5 Volt supplies. The main supply can source up to 750 mA of current, and is used to power the processor and all digital circuitry. The secondary +5 Volt supply can source up to 10 mA; it is dedicated to the onboard analog circuitry. The primary supply can be turned off by a digital shutdown signal to put the board into a low power mode in which it consumes only a few milliamps of current.

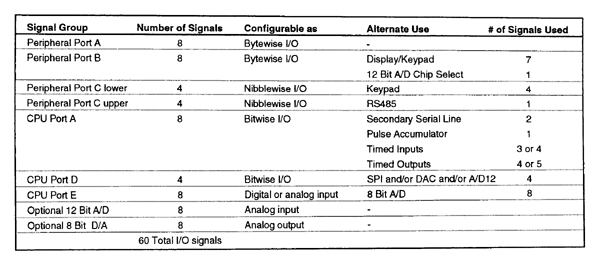

Available I/O Signals

Figure 1.2 summarizes the digital and analog I/O available on the QED Board. It specifies the origin of the signals, their type and configurability, and the number of signals dedicated to alternate uses. The following text explains the contents of Figure 1.2.

Figure 1.2 Summary of the available onboard analog and digital I/O signals and their alternate functions.

The 24 I/O lines originating at the PIA are named Peripheral Port A (PPA), Peripheral Port B (PPB), and Peripheral Port C (PPC). PPA is an 8 bit digital I/O port available for the user's application; it can be configured as either input or output.

PPB is an 8 bit digital port dedicated to the built-in keypad/display interface (PPB0 to PPB6) and to the generation of the chip select signal for the optional 12 bit A/D (PPB7). It is configured as an output port by QED-Forth.

PPC is split into two 4 bit digital I/O ports called lower PPC (PPC0 to PPC3) and upper PPC (PPC4 to PPC7). Lower PPC is used to scan the keypad. If RS485 communications is not in use, all of upper PPC is available for the user's application; it can be configured as either input or output. If RS485 is being used, one bit in upper PPC (PPC4) is dedicated to controlling the direction of data transfer, and the remaining three output bits (PPC5 to PPC7) are available for the user's application.

As shown in Figure 1.2, the 68HC11's PORTA is an 8 bit digital I/O port configurable as input or output on a bit by bit basis. These signals can also be used to implement input captures (PA0 to PA3), output compares (PA3 to PA7), and a pulse accumulator (PA7). The secondary serial port, if used, ties up two of the PORTA lines (PA3 and PA4) to implement the receive and transmit signals.

PORTD on the 68HC11 contains 4 digital I/O bits (PD2 to PD5) that implement the fast serial peripheral interface (SPI). If the SPI is not in use (which implies that the 12 bit A/D and 8 bit DAC are not on the board), these four lines are available as general purpose inputs or outputs.

The final three entries in the table in Figure 1.2 present the analog I/O ports on the QED Board. PORTE on the 68HC11 implements the 8 channel 8 bit A/D. If this A/D is not in use, PORTE can be configured as an 8 bit digital input port. The optional 8 channel (or 4 channel differential) 12 bit A/D provides 8 analog inputs, and the optional 8 channel 8 bit DAC provides 8 analog outputs. As explained in Chapter 6, pairs of DACs may be combined to achieve higher resolution digital to analog conversion.

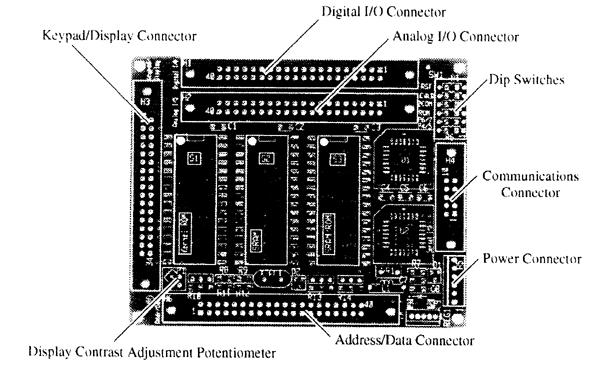

Onboard Connectors

Figure 1.3 is a simplified view of the "memory side" of the QED Board which contains the memory devices and all of the onboard connectors. The main components and connectors are labeled for easy reference. Note that the white silkscreened lettering on the QED Board itself provides a helpful legend to help you locate connectors and components.

The block diagram in Figure 1.1 gives a graphical indication of the signals that are brought out to each connector. For more detailed information, consult Appendix A in this manual which provides pin connection diagrams for each connector on the QED Board. The following discussion provides a brief overview of the functions of each connector.

The Digital I/O Connector

The 40 pin digital I/O bus brings out the signals associated with PORTA and PORTD from the 68HC11, and PPA and upper PPC from the PIA. It also brings out useful control signals including processor clocks, read/write control signals, reset and power-fail warning signals, and external interrupt request lines. Analog and digital power supplies and their respective grounds as well as an unregulated DC voltage are available on this bus.

This connector can interface directly to external digital I/O signals such as switches, control outputs, and isolated inputs and outputs. It can also be routed to a QED Protoboard or other custom board containing signal conditioning circuitry such as current-boosting darlington arrays and MOSFETs, opto-isolators, relays, and I/O devices controlled by the digital I/O ports.

The Analog I/O Connector

The 40 pin analog I/O bus brings out the signals associated with the 68HC11's 8 channel 8 bit A/D converter (labeled AN0-AN7), the optional 8 channel 12 bit A/D converter (labeled 12AN0-12AN7), and the optional 8 channel 8 bit DAC. Each DAC multiplies a reference or input voltage (labeled Vin1-Vin8) by a scale factor set by the digital code written by the processor to produce an output voltage (labeled Vout1-Vout8). A 1.5 Volt signal is available for use as a DAC reference; see Chapter 6 for details. Also available on this connector are the power signals +5V, +5VAN, V+Raw, and AGND, as well as A/D reference voltages Vrl and Vrh.

The analog connector can interface directly to external analog signals such as transducer outputs, plotters, X/Y placement devices, and audio circuitry. It can also be routed to a QED Protoboard or other custom board containing signal conditioning circuitry such as current-boosting op amps, 4-20 mA converters, and opto-isolators.

The Address/Data Connector

The 40 pin Address/Data bus brings out the processor's 8 bit data bus (D0-D7) and 16 bit address bus (A0-A15) plus the 8 page bits (PG0-PG7) that expand the memory space to 8 Megabytes. Memory read/write control signals, /Reset, and power voltages +5V, V+Raw, and DGND are also available at the connector.

This connector can routed to a custom board, or to a QED Protoboard which contains built in address decoding logic. Memory-mapped peripheral devices can communicate with the processor directly via the address/data bus. A wide variety of peripheral devices can be added in this manner, including additional memory, I/O ports, PIAs, counters, timers, and analog converters.

The Keypad/Display Connector

The 34 pin Keypad/Display connector brings out the 7 signals of PPB and the 4 signals of lower PPC that implement the keypad/display interface. The connector is designed so that a simple straight-through ribbon cable completes the connection to a 5x4 keypad and an LCD display up to 4 lines by 20 characters in size. The connections to the board-mounted contrast adjustment potentiometer for the LCD display are also brought out to facilitate the addition of a panel-mounted contrast adjustment potentiometer, if desired.

If a particular application does not use the keypad/display interface, it is possible to use the 11 relevant digital control lines (7 from PPB and 4 from PPC) as general purpose I/O signals. Note, however, that the order of the signals is "scrambled" on the connector, and that each of the 4 lower PPC inputs is "pulled up" to +5V with a 15.8 K? resistor. In general, we recommend that the signals on this connector be reserved for the keypad and display interface.

The Communications Connector

The 10 pin communications connector brings out the primary and secondary serial ports. The primary serial port can be configured as either RS232 or RS485 at standard baud rates up to 9600 baud and nonstandard rates to 125,000 baud; these rates double if the board is clocked at 16 MHz. The secondary serial port can communicate using the RS232 interface at rates up to 2400 baud (4800 baud if the board is clocked at 16 MHz). Mosaic Industries supplies a standard cable that brings the communications connector signals out to two 25 pin D-type connectors with the standard RS232 pinout.

The Power Connector

Power can be supplied to the QED Board via the 6 pin power connector. A wall-mount power supply with an integral connector that plugs into the power connector is available from Mosaic Industries. It supplies an unregulated DC voltage to the input named "6-12VDC Raw Vin". The regulated digital supply (named +5V), digital ground (DGND), analog supply (+5VAN), analog ground (AGND), and the active-low /Shutdown signal are also available on the power connector. Pulling the /Shutdown signal low puts the QED Board into a low power mode.

Figure 1.3 Diagram of the memory side of the QED Board with each of the key components and connectors labeled.

Onboard DIP Switches

Six switches make it easy to configure various options on the QED Board. The switches are located on the memory side of the board next to the communications connector (see Figure 1.3). The following table summarizes the purpose of each switch:

| Switch | Effect of Switch in the ON State |

|---|---|

| 1 | Write protects memory pages 4 and 5 (32K per page). |

| 2 | Write protects memory pages 6 and 7 (32K per page). |

| 3 | Configures the SRAM/ROM socket (S3) to accommodate a PROM. (The OFF state configures the socket to hold a RAM.) |

| 4 | Enables secondary RS232 communications hardware (serial port 2). (The OFF state configures bit 3 of PORTA for use as a general purpose digital or timer-controlled I/O line). |

| 5 | Puts the QED Board into "special cleanup mode" upon the next power-up or reset. |

| 6 | Resets the QED Board; return switch to "OFF" position to resume normal operation. |

The legend on the QED Board suggests the function of each switch. The use of the memory write-protection and RAM/PROM switches is discussed in Chapter 9. The switch that enables the secondary serial port is discussed in Chapter 11 titled "Serial Communications". The "special cleanup mode" switch forces a COLD restart to guarantee a return to a pristine software state; consult the "Interrupts and Register Initializations" chapter in the QED Software Manual for a detailed description. Toggling switch 6 ON and then OFF resets the QED Hardware.

A Chapter-by-Chapter Guide

- Chapter 2 of this manual describes the general purpose digital I/O ports available on the QED Board. Built-in driver routines that facilitate use of these ports are described.

- Chapter 3 presents a hardware perspective on 68HC11 interrupts, and suggests a step-by-step procedure that simplifies the coding of interrupt service routines.

- Chapter 4 describes the many counting and timing functions available on the QED Board. Numerous coded examples are presented.

- The serial peripheral interface (SPI) is detailed in Chapter 5. Built-in driver routines are described, and connection diagrams and a sample program are presented.

- Chapter 6 describes the analog to digital and digital to analog converters. A background discussion explains concepts such as resolution and accuracy. Simple equations are derived to convert a digital number into its equivalent analog voltage. The easy to use QED-Forth driver routines are explained. Finally, a complete coded application program and accompanying schematic allow you to convert a pair of 8 bit DACs into a single DAC with 12 bit resolution. This exciting feature allows the QED Board to address applications that require 12 bit analog input and output capabilities.

- Chapter 7 describes the built-in routines that write to the on-chip electrically erasable PROM (EEPROM).

- Chapter 8 describes a number of hardware features of the 68HC11 including external interrupts, reset conditions, operating modes, and the computer operating properly (COP) function. Step-by-step procedures are presented to help you take advantage of these functions.

- Chapter 9 presents a detailed description of the QED Board's extensive memory, and explains the features of the QED Protoboard and its built-in address decoding logic. The chapter describes the hardware write protection that makes it possible to develop an application without having to burn PROMs. A sample schematic is presented to demonstrate how to add peripheral hardware to the QED Board's address/data bus.

- The hardware aspects of the keypad and LCD display interface are described in Chapter 10.

- Chapter 11 presents a hardware perspective on the QED Board's dual serial communications ports. It discusses the RS232 and RS485 protocols and presents communications cable wiring diagrams for some common applications.

- Chapter 12 describes the built-in QED-Forth routines that set and read the optional real-time clock/calendar.

- Chapter 13 details the power requirements of the QED Board, describes the options for powering the board, presents strategies for power regulation on peripheral boards, and discusses the operation of the power-fail warning signal.

- Chapter 14 is a trouble-shooting guide that may prove useful in the event that you have hardware difficulties.

Appendices

The appendices provide a wealth of useful information organized for easy reference:

- Appendix A summarizes the pin assignments of all the connectors.

- Appendix B presents the QED Board schematics.

- Appendix C lists the 68HC11F1 hardware registers.

- Appendix D summarizes the mechanical and electronic specifications of the QED Board and QED Product Design Kit. It also suggests how to mate the QED Board to your application-specific circuit board.

- Appendix E presents the data sheet for the 82C55A PIA, and lists some additional PIA driver code.

- Appendix F is the data sheet for the 12 bit A/D converter.

- Appendix G is the data sheet for the 8 bit DAC.

- Appendix H presents some driver code for "expert" users of the 68HC11's 8 bit A/D converter.

How to Use This Manual

Each of the following chapters begins with a general description of a hardware feature, followed by implementation details and QED-Forth sample programs which clarify the discussion and facilitate access to the hardware. You are encouraged to run the programming examples and "exercise" the hardware to see how it works.

To make it easier for you to locate specified pins on the headers, consult Appendix A in this manual for pin assignments, and consult Figure 1.3 to locate the appropriate connectors. Note that the connector names are written on the legend on the memory side of the board, and the first and last pin number of each connector is indicated on the processor side of the board.

You may find it useful to photocopy Appendix A which shows the pin names and numbers of the signals on every connector. This will make it easier to locate pins when reading the manual or making connections to your QED board.

The Hardware Control Registers

The remaining chapters often refer to the processor's control registers. The names, addresses, and functions of these important registers are summarized in Appendix C of this manual (copied from pages 3-4 and 3-5 in F1). Note that QED-Forth places the registers at addresses 8000H-805FH instead of 1000H-105FH. All of the hardware functions of the 68HC11F1 are controlled by these registers.

When programming, it is convenient to refer to each control and status register by its name rather than by an address. The standard Motorola names assigned in Appendix C will be used when the registers are discussed in this manual. The first mention by name of a control register, or a bit within a register, will be in bold followed by a reference in either F1 or HC11.

The QED-Forth routine called REGISTER: allows us to associate a QED-Forth name with each register address that we need. When the name is executed, QED-Forth will automatically place the correct extended address of the register on the data stack. The REGISTER: utility will be used throughout the manual.

This QED Hardware Manual should provide you with all the information you need to successfully integrate the QED Board into your project. If after studying this material you cannot solve your problem, please Contact Us. We will do our best to help you.