Chapter 9 - Memory Mapped I/O and the Prototyping Board

The QED Board overcomes the limited 64K address space of the 68HC11 processor. It provides an 8 Megabyte address space to accommodate ample memory as well as memory-mapped peripheral devices.

The QED Board includes three memory sockets, each of which holds up to 128 kilobytes (128K) of random access memory (RAM) or programmable read-only memory (PROM). The board uses static RAM (SRAM) as opposed to dynamic RAM (DRAM). Battery-backed RAM devices can be installed which retain their data even when power is off, and onboard DIP switches can optionally write-protect segments of memory, making the memory behave like "emulated PROM". This feature eliminates the need for PROM burning during program development.

This chapter describes the QED Board's extended memory space, the Address/Data Bus, the write protection feature, and how to add memory and peripheral devices. It also describes the QED Prototyping Board and its onboard address decoding logic. This handy board makes it easy to add custom memory-mapped peripherals or I/O signal conditioning circuitry to your QED system.

A Note About Signal Names

Many of the logic signals that control memory access operations are active-low signals. The convention for naming an active-low signal is to place an overbar over the signal's name. For example, an active-low output enable signal is designated as

__ OE

and pronounced "o-e-bar". It is difficult in documents such as this to represent the overbar, so we represent active low signals by preceding them with a / ("slash") character. Thus the active-low output enable is presented in this document as

/OE

and may be pronounced either as "slash o-e" or as "o-e-bar".

The QED Board's Address Space and Onboard Memory

The 68HC11 processor has a 16-bit address bus comprising Ports B and F on the processor. Thus it can address 216 bytes, or 64 Kbytes, and the processor's assembler instructions can handle 16-bit addresses. This amount of memory is too limited for many applications, so the QED hardware and software have been designed to increase the memory space to 8 Megabytes. This is accomplished by designating an 8-bit port on the processor (Port G) as a "page latch" that provides 8 additional address lines.

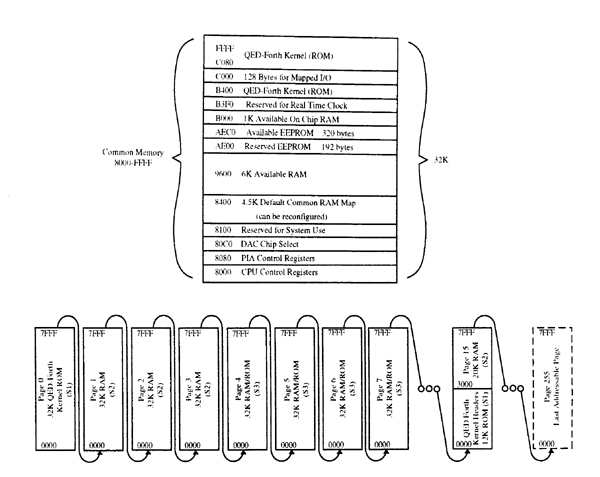

The memory expansion is accomplished using a unique memory map that maximizes run-time efficiency. The on-board memory map is pictured in Figure 9.1. The bottom 32K of the processor's address space at addresses 0000-7FFFH is "paged memory", and the page latch allows up to 256 pages of memory to be selected (256 pages X 32 Kbytes/page = 8 Megabytes of memory). The page latch is used to select which memory device is active, and the processor's address lines are used to address a particular location within the selected memory device.

Figure 9.1. Diagram of the QED Board memory map. The 32K of "common memory" at addresses 8000H to FFFFH (the upper half of the processor's memory space) is rapidly accessible without a page change. Up to 256 pages (32K per page) occupy the "paged memory" at addresses 0000 to 7FFFH. If 128K memories are installed in sockets S2 and S3, the common memory as well as pages 0-7 and 15 are present on the QED Board.

The top 32K of the 68HC11's memory at addresses 8000-FFFFH is called the "common memory"; it is always accessible regardless of the contents of the page latch. The most frequently called kernel routines as well as the stacks and user area reside in the common memory and are accessible without a page-change operation. Most words call either kernel routines or other words compiled on the same page as the calling word. The result is that very few page changes are needed when running a program, and this maximizes execution speed.

The QED-Forth memory operations (for fetching, storing, moving memory, performing address calculations, and managing the heap memory) treat the paged memory as a single contiguous area. As suggested by the connecting arrows in Figure 9.1, the memory location after the last address (7FFFH) on any page is the first location (0000H) on the following page. The basic memory operations are all smart enough to know how to handle page changes and how to deal with page boundaries.

Available PROM and RAM on the QED Board

The QED Board has 3 memory sockets labeled S1, S2, and S3. Each socket has an alternate name; S1 is also called the "kernel ROM" socket, S2 is known as the "SRAM" socket, and S3 is called the "SRAM/ROM" socket. Each socket can accommodate a memory device ranging from 32 Kbytes to 128 Kbytes.

Socket S1 accommodates the QED-Forth kernel ROM which holds the development system as well as the runtime libraries. This ROM must be present for the QED Board to function.

Socket S2 holds a 32K or 128K static RAM (SRAM), and at least 32K of RAM must be present in this socket for the QED Board to operate. The memory in this socket cannot be write-protected. If a 32K RAM is installed in S2, the onboard logic places 20K of it on page fifteen (0FH) at addresses 3000H to 7FFFH and the remainder in common memory at addresses 8100H-ADFFH (but note that 8100H-83FFH is reserved for use by QED-Forth). An additional 1K of common memory is available at addresses B000H-B3FFH; this is the 68HC11's on-chip RAM. The total amount of common RAM available to the programmer (including the 68HC11 on-chip RAM and excluding the common RAM reserved by QED-Forth) is 11.5K. If a 128K RAM is installed in socket S2, the three 32K pages numbered 1, 2, and 3 are also available.

Socket S3 is called the "SRAM/ROM socket". It accommodates either static RAM (typically during program development) or PROM (typically in your final product). During program development and debugging, a 128K battery-backed RAM is typically installed in this socket. The memory is addressed at pages 4, 5, 6, and 7, and each page contains 32 Kbytes. Turning onboard DIP switch #1 ON write-protects pages 4 and 5, and turning DIP switch #2 ON write-protects pages 6 and 7. This socket is an ideal location for the memory areas such as the dictionary and names area that will end up as PROM in the final system. During program development, code can be compiled into the RAM in this socket, and the memory can be write-protected to emulate a PROM. When the application is completely debugged, the contents can be burned into a PROM, and the PROM can be plugged into the socket. Turning dip switch #3 ON configures the socket for a PROM, and the system is complete. The PROM size can be 32K (page 4 only), 64K (pages 4 and 5), or 128K (pages 4, 5, 6, and 7).

Appendix A in the QED Software Manual explains the memory map in more detail.

Write-Protection Transforms Memory Pages to Emulated ROM

The QED Board implements a memory write-protection scheme that speeds program development by eliminating the need for PROM burning. The QED Developer Package and QED Product Design Kit come with a 128K battery-backed RAM installed in the SRAM/ROM socket which implement pages 4, 5, 6, and 7. Two DIP switches on the board control the write-protection of these pages. When write-protected, the onboard battery-backed RAM behaves just like ROM: it maintains its data when the board is powered down, and its contents cannot be altered by the processor because the write control signals are inhibited by the board's logic. The onboard memory pages may be write-protected or un-protected at any time by just flipping a DIP switch.

DIP switches #1 and #2 control the write-protection as summarized in the following table:

| Switch 1 | Switch 2 | Pages 4 and 5 | Pages 6 and 7 |

|---|---|---|---|

| OFF | RAM | ||

| ON | Write-protected memory | ||

| OFF | RAM | ||

| ON | Write-protected memory |

That is, turning DIP switch #1 ON write-protects pages 4 and 5, and turning DIP switch #2 ON write-protects pages 6 and 7.

Testing the Write-Protection Feature

To test the write-protection capability, let's turn switch 1 OFF so that pages 4 and 5 are modifiable RAM and use the ! (store) command to save a number to an address on page 4, and then verify that the number was saved. Then we can write-protect page 4 and verify that store operations have no effect, showing that the write-protected memory cannot be altered. The following code verifies the correct operation of the write-protection feature:

\ First turn DIP switch #1 OFF so that pages 4 and 5 are not write-protected. HEX 1234 2000 4 ! \ store 1234 into location 2000 on page 4 2000 4 ? \ check that 1234 is stored at location 2000 \ Write protect pages 4 and 5 by turning DIP switch #1 ON. 2000 4 ? \ reassure yourself that 1234 is at 2000 4321 2000 4 ! \ attempt to store 4321 at 2000 on page 4 2000 4 ? \ 1234 is still stored at location 2000 so \ storing 4321 there did not work, as expected. \ Turn DIP switch #1 OFF so that pages 4 and 5 are no longer write-protected 2000 4 ? \ check again that 1234 is at 2000 4321 2000 4 ! \ try storing 4321 at 2000 on page 4 again 2000 4 ? \ this reveals that 4321 was \ successfully stored this time, as expected.

Repeating this exercise using pages 6 and 7 (controlled by DIP switch #2) will demonstrate that these pages can also be write protected.

The "Program Development Techniques" chapter in the QED Software Manual explains how to use the write-protection feature to great advantage while developing your application.

Burning An Application PROM To Move Into Production

The "Program Development Techniques" chapter in the Software Manual explains how to install an autostart vector using the PRIORITY.AUTOSTART routine so that your program automatically starts up when power is applied, and how to burn an application PROM when you have finished debugging your program. The chapter in the Software Manual titled "Putting It All Together: A Turnkeyed Application Program" provides further details about creating an autostarting application PROM.

After burning your application PROM, it is easy to create a "production" version of your instrument. Simply power down the board, remove the RAM from socket S3, plug the newly burned PROM into S3, and flip the DIP switch #3 (the S3 RAM/ROM switch) to the ON position. Power up the QED Board and it will automatically run your application. Replicate your PROMs and you're in production!

Address/Data Bus Signals

The processor communicates with memory and memory-mapped peripherals via an 8-bit bi-directional data bus. To "write" or "store" to an external device, the processor places the address of the device on the extended address bus, places data on the data bus, and activates control signals that cause the device to accept the data. To "read" or "fetch" from an external device, the processor places the address of the device on the extended address bus, activates control signals that cause the device to place its output data on the data bus, and the processor then accepts this data into an internal register via the data bus.

The 68HC11F1 selects the external memory locations to be accessed by outputting a 24-bit "extended address" comprising the processor's 16 address bits plus the 8 page bits. The external device is activated by a "chip select" signal that is typically generated by hardware logic; the chip select signal is asserted when a specified bit pattern appears on all or part of the extended address bus. The next section of this chapter presents an example (the addition of a 32K memory device) to clarify this concept.

The physical pins that implement the QED Board's paged address/data bus are located on the 40 pin Address/Data Bus connector as shown in Appendix A. The 8 page latch bits, named PG0...PG7, are located at pins 1 through 8 on the Address/Data Bus. The 16 address lines, named A0...A15, are located at pins 9 through 24 on the Bus. The 8 bi-directional data lines, named D0...D7, are located at pins 25 through 32 on the Bus. The remaining 8 pins on the connector are +5v, V+raw, digital ground (see the Power Chapter), and control signals named R//W (read/active-low write), E (E-clock), /WE (active-low write enable), /OE (active-low output enable) and /RESET (active-low reset).

Control Signals

Hardware devices interfaced to the QED Board via the Address/Data bus use control signals to coordinate the exchange of information on the data lines. The two most basic control signals are R//W (read/active-low write) and E (E-clock), both of which are generated by the 68HC11 processor. The R//W signal is low when the processor is writing to external memory, or between the successive 8-bit writes that make up a 16-bit store operation. The signal is high at other times. R//W is often active low at times when the address and data lines are not stabilized or valid for writes to memory, and for this reason the E-clock is also needed to control the timing of memory accesses.

The E-clock is a square wave generated by dividing the external crystal oscillator signal by 4, yielding a 2 MHz signal if the onboard crystal frequency is 8 MHz, or a 4 MHz signal if the crystal frequency is 16 MHz. When the E-clock is high, the processor's address and data lines are stable and available to access memory. When the E-clock is low, the processor is setting up its address lines and/or performing an internal non-memory operation.

Peripheral devices manufactured by Motorola are typically controlled by the combination of R//W and E. However, memories and many devices made by other manufacturers are controlled by a different pair of signals that are active only when the processor is able to read or write to the device (that is, active only when the address and data lines are valid). These control signals are named /OE (active-low output enable) and /WE (active-low write enable). They are generated in the on-board programmable logic device as combinations of the E and R//W signals.

The /OE signal is active low when the processor is reading an external device. When it is low (if the peripheral is also "selected"), this signal tells a selected external device to enable its output drivers so that the processor can read the data that it is putting out. /OE is formed as the logical NAND of E with R//W. It can be thought of as an inverse-logic version of the R//W signal that is synchronized with the E clock.

The /WE signal is active low when the processor is writing to an external device. When it is low, this signal tells a selected external device to accept the data that the processor has put on the data bus. /WE is formed as the logical NAND of E with an inverted version of R//W. The /WE signal can be thought of as a signal that is synchronized with the E clock and that has the same polarity as R//W .

These E, R//W, /OE, and /WE signals facilitate access to a wide variety of peripheral hardware devices.

The remaining control signal on the Address/Data Bus is named /RESET (active-low reset). This signal is low when the 68HC11 is being reset. It may be used by add-on boards to sense a CPU reset condition or to force a system reset. If the add-on board is designed to force the processor to reset by driving /RESET low, it must keep the signal low for at least 4 E-clock cycles, corresponding to 2 microseconds with an 8 MHz crystal frequency (HC11 p.5-10).

The control signals E, R//W, /WE, /OE and /RESET are also accessible on the Digital I/O and Control bus (see Appendix A).

How to Interface Memory-Mapped Peripherals

There are two ways the QED board can be interfaced with peripheral devices:

- Digital I/O ports can be used to generate chip selects, write data to the peripheral, and accept the peripheral's output data, or

- The peripheral can be treated as if it were one or more memory locations, with the chip select signal generated based on the address and page bus, and data exchanged using the data bus.

I/O Mapped Peripherals

Method 1 involves controlling peripherals using I/O port signals. This method is easy to implement, although it does require you to dedicate scarce I/O lines to control the peripheral. For example, 9 output port bits could be used to control an 8-bit digital-to-analog converter. Eight port bits could output the 8-bit value to the D/A, and the ninth port bit could be a control and chip select signal that tells the D/A to update its analog output based on the current digital input.

Memory Mapping

Method 2 is called "memory mapping", and is discussed in detail here. Memory mapping is the most flexible way to add peripherals including RAM, ROM, and a variety of input/output devices.

A "chip select" signal is required to map a peripheral device onto the memory space. Decoding logic must be designed to generate the chip select signal based on the address and page outputs of the processor. There is a trade-off between the complexity of the decoding logic and the amount of memory space that the peripheral occupies. For example, if a peripheral is to be addressable only at a single byte location in a single page, then all 24 bits of the extended address bus must be decoded to generate the chip select signal. If, on the other hand, a peripheral is allowed to occupy an entire page of memory, then only 9 bits (the 8 page bits plus A15) are sufficient to generate the chip select signal. Thus, even if a peripheral can be accessed as a single byte mapped onto the memory space, it is frequently advantageous to allow it to occupy an entire page (or even several pages) to simplify the decoding hardware. The large address space of the QED Board makes this an appealing option.

Peripherals that may be memory mapped onto the QED board include digital to analog or analog to digital converters, UARTs, additional latched I/O ports, high current relay drivers, displays, and disk drives. The following example describes how to add memory to the QED Board. Other peripherals are added in similar fashion.

The QED Prototyping Board offers an easy way to add memory mapped devices to your system. This board includes address decoding logic that generates chip select signals for you. The Prototyping Board is described in detail later in this chapter.

Adding a 32K Memory Device

Adding a 32K page of static RAM or PROM memory to the QED board is very easy. The memory device should be CMOS or HCMOS compatible with access time of 150 ns or faster (100 ns or faster if your QED Board is clocked at 16 MHz). All of the signals needed to interface the memory, except the chip select, are available on the 40-pin Address/Data Bus (see Appendix A). Thus adding the memory simply involves decoding the page to generate a chip select, and connecting the address, data, and control signals to the memory chip.

To generate an active-low chip select signal for the page-mapped RAM, logic is required that outputs a low signal when the specified page is addressed, and outputs a high signal at all other times. For example, if the RAM is to reside at page 10H, the logic must generate an active-low signal whenever the binary pattern for 10H (0001 0000B) appears on the page bus AND address bit A15 is low (indicating that paged memory, not common memory, is being accessed).

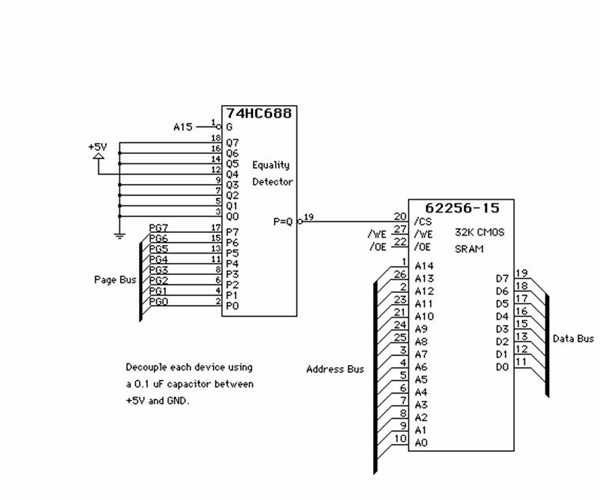

An 8-bit equality detector such as the 74HC688 can be used to generate the chip select signal. The inputs to the equality detector in this example are a set of 8 hard-wired signals representing the binary code for page 10H (0001 0000B) as well as the 8 page bits PG0...PG7. Conveniently, the 74HC688 has an additional active-low "enable" input that we connect to address bit A15. When A15 is low and the processor's page bits match the hard-wired pattern for page 10H, then the equality detector outputs an active low chip select that activates the RAM. This circuit is illustrated in Figure 9.2. Simply changing the hard-wired page pattern allows the memory to be mapped onto any specified page. Be careful, however, not to overlap existing memory pages 0 through 7 or twelve through fifteen. Doing so would cause contention on the data bus that could damage the components on the board.

To map larger memory devices onto the QED system, simply eliminate some low-order page bits from the decoding logic so that the chip select is active over several pages. For example, a 128 Kbyte memory can be mapped onto pages 10H, 11H, 12H, and 13H by replacing the PG0 and PG1 inputs to the equality detector in Figure 9.2 with hard-wired ground connections. Then the chip select signal is active over a 4-page range, and PG0 and PG1 can serve as the two highest-order address inputs to the 128K memory device. Note that processor address signal A15 is not wired directly to the memory device. Rather, A15 is used by the decoding logic to distinguish accesses of common memory (A15 high) from accesses of the paged memory (A15 low).

Figure 9.2 Circuit that memory maps a 32 Kbyte CMOS static RAM (62256LP-15) onto page 10H using an 8-bit equality detector (74HC688) to generate a chip select signal.

Memory Mapping Peripherals onto the Common Page

The above examples map peripherals onto specified pages in the address space. While this is a good strategy for most applications, it does require QED-Forth to execute a page-change to access the peripheral. Peripherals that must be accessed very rapidly may be mapped onto the common page to avoid the slight speed penalty (about 14 microseconds) associated with changing pages.

On QED Boards manufactured after January 1993, the 128 bytes located at addresses C000H through C07FH are reserved for your common-memory-mapped peripheral devices. That is, you may decode addresses C000H through C07FH to generate chips select signals for your peripheral devices.

The QED Prototyping Board

The QED Prototyping board makes it easy to connect your custom hardware to the QED Board. The QED Protoboard is exactly the same size as the QED Board (3.2" x 4.0"), and its standoff holes are aligned with the QED Board to facilitate board stacking. It is designed to accommodate both wire wrap and soldered prototype circuits. This section describes the versatile features of the Protoboard.

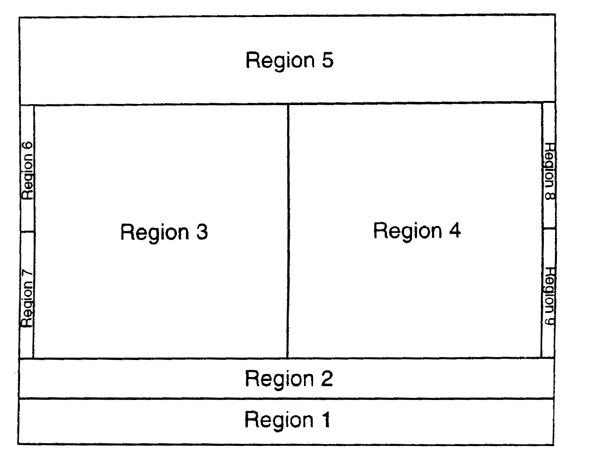

The QED Protoboard can be divided into 9 unique regions as shown in Figure 9.3.

Figure 9.3. Regions of the QED Prototyping Board.

Region 1 provides an easy way to connect any of the QED Board's three 40 pin connectors to the protoboard. The 40 pin connectors include the Analog I/O connector, the Digital I/O connector, and the Address/Data Connector. Typical uses of the protoboard include adding signal conditioning circuitry to the QED Board's A/D or D/A converters, interfacing opto-isolators or high current drivers to digital inputs and outputs, and adding additional memory-mapped hardware.

Each QED Product Design Kit is shipped with the protoboard connected to the QED Board's Address/Data Bus. In this configuration, memory mapped hardware is easily interfaced to the QED Board. The integrated circuit installed on the protoboard is a PAL (Programmable Array Logic device) programmed to provide 10 memory mapped chip select output signals. These chip select signals are compatible with a broad range of devices which require active HIGH or LOW enable signals. The signals are accessible via a row of holes alongside the PAL. The following table lists the name of each signal, the page or pages selected (in decimal and hexadecimal notation), and the polarity of the signal:

| Hole | Selects Page(s) | Active State |

|---|---|---|

| A | 255 (FFH) | LOW |

| B | 254 (FEH) | LOW |

| C | 253 (FDH) | LOW |

| D | 252 (FCH) | LOW |

| E | 248-251 (F8-FBH) | HIGH |

| F | 244-247 (F4-F7H) | LOW |

| G | 240-243 (F0-F3H) | LOW |

| H | 236-239 (EC-EFH) | LOW |

| I | 232-235 (E8-EBH) | LOW |

| J | 224-231 (E0-E7H) | LOW |

These chip selection signals make it easy to add memory mapped devices to the QED Board. For example, if we use the Prototyping Board to add a 32K RAM device, the 74HC688 chip shown in Figure 9.2 is no longer needed. The RAM can be mapped onto the top page of memory (page FFH) by connecting the chip select output at hole A to the /CS input pin at pin 20 on the 62256 RAM device. Similarly, a 128K memory device could be addressed at pages F0-F3H by using the signal at hole G as the chip select input.

A peripheral device that requires an active high chip select should use the signal at hole E. Otherwise, such a device could be selected by simply inverting one of the active-low chip select signals.

The PAL can only be used when the Address/Data bus is connected at Region 1. The PAL must be removed if a connector other than the Address/Data bus is attached to the protoboard at Region 1, and failure to remove the PAL in this circumstance could damage the device.

In addition to providing pre-programmed chip select signals, Region 1 gives access to the attached 40-pin bus via two parallel rows of holes alongside the 40 pin header. These make it easy to connect soldered circuitry to the bus signals.

Region 2 provides two rows of holes to accommodate any sized dual row connector (up to 76 pins) that you may need.

Region 3, named the "triples" area, provides 6 columns of three holes connected together. DIP style sockets or devices can be installed in this region and the interconnected holes facilitate point to point soldering. This area is also convenient for installing discrete devices such as resistors, capacitors, and transistors. When placing a device in this area, be aware of the pre-connected hole "triples" so that you do not accidentally short device leads together.

Region 4 is an open region of plated through-holes on a 0.1" grid. This region can accommodate any device compatible with a 0.1" grid including DIP and PLCC integrated circuits.

Region 5 consists of 4 rows of enlarged holes. These holes are large enough to accommodate screw terminal connectors. A common configuration is to install a screw terminal block in Region 5 (to connect to external signals), place signal conditioning circuitry in Regions 3 and 4, and connect the QED Board Digital or Analog I/O Bus to the header in Region 1 (in this case the PAL should be removed from its socket).

Regions 6 through 9 are called "rails". These rails are used to distribute a common signal, for example power or ground, to a row of holes. Each rail is connected to an access hole in Region 1. The legend denotes the rails and access holes as R1, R2, R3, and R4. For example, by connecting +5 Volts and ground to R1 and R2 respectively, your QED Protoboard can cleanly distribute power and ground rails for easy connection to circuitry. Also note that three holes on the outer end of each rail have been enlarged; the legend marks these with a bar. These large holes can accommodate TO-220 style power regulators (for example an LM7805). A properly oriented regulator can then directly drive a power rail.

We recommend that you carefully examine the QED Protoboard before using it. Become familiar with the pattern of pre-connected holes. Used properly, the QED-Protoboard can accommodate a broad range of circuitry.

Summary

The QED board has an 8 Megabyte address space accessed via a 16-bit address bus and an 8-bit page bus. The board hosts three memory devices of up to 128K each. Pages 4, 5, 6, and 7 are write-protectable RAM that, with the flip of a switch, may be write protected. This feature eliminates the need for PROM burning during program development.

Memory mapping is a simple and flexible way to add peripheral devices to the QED Board. Peripherals are interfaced to the address/data/control bus using the control signals E, R//W, /WE, and /OE, and by decoding the address and page bits to generate a unique chip select signal for the device. Data is then exchanged between the QED Board and peripherals via the data bus.

The QED Prototyping Board facilitates the addition of peripheral devices and signal conditioning circuitry to your QED system. It includes address decoding circuitry that makes it easy to interface memory-mapped devices to the QED Board.