Getting to Know Your Hardware

PDQ Board Starter Kit

If you purchased a PDQ Board Starter Kit, you should have received the following:

- A PDQ Board single board computer (SBC) with Real-Time Clock (Part No. PDQB-RB);

- A Docking Panel (Part No. DP);

- A 9-pin PC Serial Cable (Part No. PCC9-232);

- An 8-26 volt Power Supply (Part No. PS-8V);

- A CD-ROM containing:

- The Mosaic IDE Plus™ C language programming environment and the Mosaic Terminal program;

- Program examples; and

- Documentation PDF files for offline use.

If you are missing any of these items, please contact us immediately.

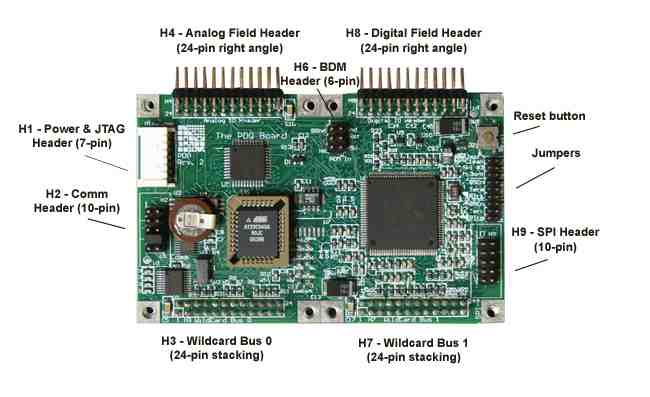

A tour of the headers and jumpers

Figure 1-3 shows a photo of the top side of the 4” x 2.5” PDQ Board, and diagrams the positions of the headers and jumpers. The large chip on the right is the 9S12 (HCS12) microcontroller.

You can find more detailed physical dimensions here.

Configuring jumpers on the PDQ Board

| Jumper | Label | Description |

|---|---|---|

| J1 | Clean | Puts the PDQ Board into special cleanup mode on the next power-up or reset. To return the PDQ Board to its pristine, right-from-the-factory condition, install this jumper, press the Reset Button, and then remove the jumper. |

| J2 | SPI #2 | If installed, configures the board as the bus master of SPI2, bus slave of SPI1. SPI1 and SPI2 may be reserved for inter-processor communications in multi-processor systems such as the PDQScreen. |

| J3 | NoBoot | If installed, disables the processing of Boot Vectors. Typically not installed. |

| J4 | 1 485En | If installed, enables RS485, disables RS232 on the Serial1 port |

| J5 | 1 Term | If installed with J4, provides RC termination for the RS-485 communications link on Serial 1 by connecting a 120 Ohm resistor in series with a 0.1 micro-Farad capacitor across the RS485 line. |

| J6 | 1 RTrm | If installed with J4 and J5, shorts out the capacitive termination on RS485-1 serial port, resulting in purely Resistive termination. |

| J7 | 2 485En | If installed, enables RS485, disables RS232 on the Serial2 port |

| J8 | 2 Term | If installed with J7, provides RC termination for the RS-485 communications link on Serial 2 by connecting a 120 Ohm resistor in series with a 0.1 micro-Farad capacitor across the RS485-2 line. |

| J9 | 2 RTrm | If installed with J7 and J8, shorts out the capacitive termination on RS485-2 serial port, leaving the Resistive termination intact. |

Power header

The PDQ Board requires that a regulated +5VDC supply be connected to at least one of the following headers: the power header (H1, pin 3), the digital field header (H8, pin 2), or one of the Wildcard module headers (H3 or H7, pin 2). If Wildcards are mounted to the PDQ Board some of them may additionally require that a greater DC voltage of +8 to +26 VDC, designated V+Raw, be applied to to pin 1 of the power header (or to pin 4 of H3, H4, or H7). The power header also hosts pins used for JTAG programming of a CPLD on the board, but you will generally not need to use this facility. The following table provides the power header’s pinout:

| H1: Power Header | |

|---|---|

| Pin | Signal |

| 1 — | V+RAW (+8 to +26 VDC) |

| 2 — | GND |

| 3 — | +5 VDC |

| 4 — | TDI for JTAG programming |

| 5 — | TMS for JTAG programming |

| 6 — | TCK for JTAG programming |

| 7 — | TDO for JTAG programming |

| Note: V+RAW is needed only if certain Wildcards are used. Pins 4-7 are generally not used. | |

Communications header hosts Serial1 and Serial2 ports

The Serial 1 and Serial2 ports can be independently configured for RS-232 or RS-485 communications at standard rates up to 115,200 baud and nonstandard rates to 1,250,000 baud. Typically, the Serial1 port is used as the programming interface, leaving the Serial 2 port to be dedicated to peripheral devices such as a printer or a smart sensor. Both serial ports bring out their transmit and receive pins (TxD and RxD), as well as their RS485 transceiver pins (XCV+ and XCV-) to the communications header. The following table illustrates the Comm header pinout, and points out the differences between the PDQ Board Comm header and the Comm header on the Docking Panel.

| H2 on PDQ Board: Communications Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| /TxD1 | —1 | 2— | /RxD1 |

| DGND | —3 | 4— | RS485 XCV2+ |

| RS485 XCV1- | —5 | 6— | RS485 XCV1+ |

| /TxD2 | —7 | 8— | /RxD2 |

| DGND | —9 | 10— | +XCV2- |

| Note: This pinout differs from that of the comm header on the Docking Panel itself: on the Docking Panel pin 4 is connected to DGND and pin 10 is connected to +5V. | |||

| H1 on Docking Panel: Communications Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| /TxD1 | —1 | 2— | /RxD1 |

| GND | —3 | 4— | GND |

| RS485 XCVR- | —5 | 6— | RS485 XCVR+ |

| /TxD2 | —7 | 8— | /RxD2 |

| GND | —9 | 10— | +5V |

| Note: This pinout differs from that of the PDQ Board pinout: on the PDQ Board pin 4 is connected to XCV2+ and pin 10 is connected to XCV2-. | |||

SPI header hosts SPI1 and SPI2 ports

Serial Peripheral Interface (SPI) ports SPI1 and SPI2 are available for inter-processor communications on multi-processor systems such as the PDQScreen, and are brought out to a dedicated 10-pin SPI header. If multi-processing is not required, these fast synchronous serial ports can be used to interface to other peripheral devices. The byte-sized messages are transmitted and received via the MOSI (Master Out/Slave In) and MISO (Master In/Slave Out) pins, and are synchronized by the SCK clock signal. The /SS (active-low slave select input) is typically used to enable data transfers by slave devices when it is active low. After each startup, one of these two SPI ports is configured as a bus master, and the other as a slave. The “SPI#2” jumper determines this configuration: if the jumper is not installed, SPI2 is the bus master and SPI1 is the slave. If the jumper is installed, SPI1 is the master and SPI2 is the slave.

| H9: SPI Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| /SS1 | —1 | 2— | /SS2 |

| SCK1 | —3 | 4— | /SCK2 |

| MOSI1 | —5 | 6— | MOSI2 |

| MISO1 | —7 | 8— | MISO2 |

| DGND | —9 | 10— | /XIRQ |

Note that a common ground connection is necessary among the devices that communicate via the SPI. The accompanying table illustrates the SPI header pinout.

Digital field header

| H8: Digital Field Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| GND | —1 | 2— | +5V |

| PM5 | —3 | 4— | PM4 |

| PM3 | —5 | 6— | PM2 |

| PM1 | —7 | 8— | PM0 |

| PP7 | —9 | 10— | PP6 |

| PP5 | —11 | 12— | PP4 |

| PP3 | —13 | 14— | PP2 |

| PP1 | —15 | 16— | PP0 |

| (TxD4) PT7 | —17 | 18— | PT6 (RxD4) |

| (TxD3) PT5 | —19 | 20— | PT4 (RxD3) |

| PT3 | —21 | 22— | PT2 |

| PT1 | —23 | 24— | PT0 |

The PDQ Board’s digital field header provides access to the 8-line PORTP PWM port, the 8-line PORTT Enhanced Capture/Timer (ECT) port, and 6 of the 8 lines of the PORTM general purpose digital I/O port (the remaining 2 PORTM pins are available on the analog field header). The operation of these signals is described in the Digital and Timer-Controlled I/O chapter of this document. If convenient, you may power the PDQ Board through the digital field header’s power pins.

Enhanced Capture/Timer pins PT4 - PT7 can provide two logic-level serial ports in addition to the two built-in RS-232 serial ports by including the Soft_UART library in your application. For more information, see: Implementing Logic-Level Serial Ports

Analog field header

| H4: Analog Field Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| AGND | —1 | 2— | +5VAN |

| GND | —3 | 4— | V+RAW |

| SCL | —5 | 6— | SDA |

| PM7 | —7 | 8— | PM6 |

| AN15 | —9 | 10— | AN14 |

| AN13 | —11 | 12— | AN12 |

| AN11 | —13 | 14— | AN10 |

| AN9 | —15 | 16— | AN8 |

| AN7 | —17 | 18— | AN6 |

| AN5 | —19 | 20— | AN4 |

| AN3 | —21 | 22— | AN2 |

| AN1 | —23 | 24— | AN0 |

The PDQ Board’s analog field header provides access to the 16 analog-to-digital (ATD) converter input pins AN0-AN15, as well as the I2C serial port pins SCL and SDA, and the upper 2 bits of the PORTM general purpose digital I/O port. The AN0-15 pins perform analog-to-digital conversion with 8- or 10-bit resolution, or they can be configured as digital input pins. The AGND pin is tied to the ground plane of the board right at pin 1 of this header and also connects to VRL (the low reference input) of the ATD converter on the HCS12 processor, so it provides a good reference for analog inputs. The +5VAN signal is a carefully decoupled version of the +5V supply that is connected to VRH (the high reference input) of the A/D converter on the HCS12 processor. V+RAW is simply wired to the like-named pins on the Wildcard bus headers and the power header. The table to the left illustrates the pinout.

Wildcard I/O expansion interface

The PDQ Board’s Wildcard Port Headers (identified as Port 0 and Port1) allow you to mount up to 8 Wildcards simultaneously on a single PDQ Board. Wildcards mounted on Port0 have module addresses 0 through 3, and Wildcards mounted on Port1 have module addresses 4 through 7. The two headers bring out the same signals with the exception of the /MOD.CS signal on pin 11 which distinguishes the two stacks. The Wildcards mount onto the PDQ Board via the dual 24-pin stack-able go-through headers, with up to 4 Wildcards allowed per stack. Ribbon cabling is not allowed on the Wildcard bus, as it may compromise the integrity of the signals on the control bus. The 24-pin Wildcard headers provide the following signals:

| H3 & H7: Wildcard Port0 & Port1 Headers | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| GND | —1 | 2— | +5V |

| /IRQ | —3 | 4— | V+RAW |

| SEL1/XMIT- | —5 | 6— | SEL0/XMIT+ |

| MOSI/XCV- | —7 | 8— | MISO/XCV+ |

| /RESET | —9 | 10— | SCK |

| /MOD.CS | —11 | 12— | 16MHz |

| E | —13 | 14— | R/W |

| /OE | —15 | 16— | /WE |

| AD7 | —17 | 18— | AD6 |

| AD5 | —19 | 20— | AD4 |

| AD3 | —21 | 22— | AD2 |

| AD1 | —23 | 24— | AD0 |

BDM header

The PDQ Board’s BDM (Background Debug Mode) 6-pin header enables the connection of a “dongle” that attaches to your desktop PC to enable assembly-level debugging of code in the HCS12 processor. Caution: The PDQ Board’s operating system in onchip flash is write-protected to prevent accidental erasure during normal use. However, it is possible to completely erase the contents of all flash memory on the HCS12 processor using the BDM tools from third party suppliers. Doing this would erase the operating system and render the board “brainless”, so proceed cautiously before attempting erase operations using the BDM interface.

| H6: BDM Header | |||

|---|---|---|---|

| Signal | Pins | Signal | |

| BGND | —1 | 2— | GND |

| NC | —3 | 4— | /RESET |

| NC | —5 | 6— | +5 |

This BDM header has a standard pinout defined by Motorola and supported by third party debugger vendors such as P&E Microcomputer Systems. The table summarizes the pinout.

See also → Using Your Docking Panel