Memory Allocation

The PDQ Board Lite is a low cost prototyping board, development platform and production board for instrument control and automation. The heart of this development board is its 9S12/HCS12 MCU. All of the memory on the PDQ Board Lite resides on the microcontroller chip, which has plenty of on-chip memory for programming, including:

- 336 KB (kilobytes) of Flash memory to hold an application program and libraries;

- 9 KB of RAM for variables and data structures; and,

- 384 bytes of EEPROM for storage of non-volatile but changeable data such as calibration constants.

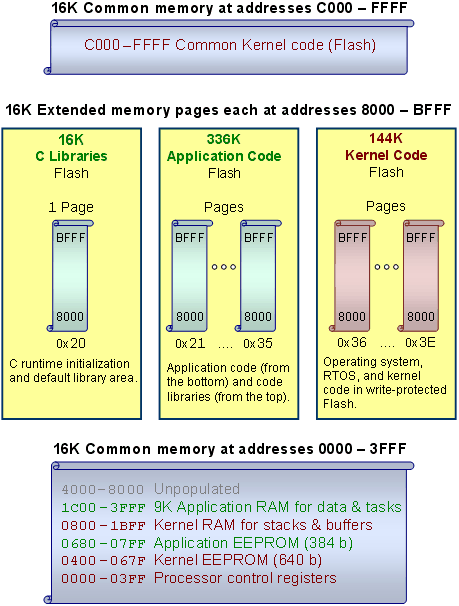

The board uses a paged memory scheme to expand its address space. The Flash memory is partitioned into thirty one 16 KB pages and allocated among operating system use (RTOS) and your application as follows:

| PDQ Board Lite Memory Allocation | ||||

|---|---|---|---|---|

| System Memory | ||||

| Page | Address | Size | Type | Use |

00 | 0000 – 03FF | 1 KB | RAM | Processor control registers |

00 | 0400 – 067F | 640 B | EEPROM | Kernel vectors and structures |

00 | 0800 – 1BFF | 5 KB | RAM | Kernel stacks, buffers and task areas |

36 - 3E | 8000 – BFFF | 144 KB | Flash | Operating system kernel code |

00/3F | C000 – FFFF | 16 KB | Flash | Common kernel code (addressed at pages 00 or 3F) |

| Application Memory | ||||

| Page | Address | Size | Type | Use |

00 | 0680 – 07FF | 384 B | EEPROM | Application EEPROM variables |

00 | 1C00 - 3FFF | 9 KB | RAM | Application data and task areas |

20 | 8000 – BFFF | 16 KB | Flash | C runtime initialization |

21 – 34 | 8000 – BFFF | 320 KB | Flash | Application code |

35 | 8000 – BFFF | 16KB | Flash | Mosaic driver firmware |

| Notes: 1. The RAM from 0x0800-0x1BFF is used for default queued serial buffers, stacks, a small Forth compile area including variable, dictionary, names areas, and Forth heap.2. Applications may use queued serial, which uses four 64-byte buffers that are located in the system RAM area. | ||||

Figure 1 below shows the memory map as paged memory. The 64 KB address spaces is illustrated vertically, with address 0x0000 at the bottom and 0xFFFF at the top. Addresses in the range 0x8000-0xBFFF are replicated on multiple pages of Flash memory, providing a total of thirty-one, 16 KB pages.

See also → Getting to Know Your Hardware