# MSCAN Block Guide V02.15

Original Release Date: 19 MAY 1998 Revised: 15 JUL 2004

Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and a registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

©Motorola, Inc., 2001

## **Revision History**

| Version<br>Number | Revision<br>Date | Effective Date | Author | Description of Changes                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------------------|------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V02.08            | 17 JUL<br>2001   | 17 JUL<br>2001 |        | - 1st offical version by Technical Publishing                                                                                                                                                                                                                                                                                                                                              |  |  |

| V02.09            | 10 JUL<br>2001   | 10 JUL<br>2001 |        | - Updated according to requirements of SRSv3 - Corrected footnote 1 in INITRQ description.                                                                                                                                                                                                                                                                                                 |  |  |

| V02.10            | 10 OCT<br>2001   | 10 OCT<br>2001 |        | - Replaced all references w.r.t. new family name HCS12.                                                                                                                                                                                                                                                                                                                                    |  |  |

| V02.11            | 22 OCT<br>2001   | 22 OCT<br>2001 |        | <ul> <li>Corrected figure title and note of CANTIER.</li> <li>Corrected local enable register names in table 4-4 'CRG Interrupt Vectors'.</li> <li>Updated block diagram.</li> <li>Corrected section 'Description of Interrupt Operation'.</li> </ul>                                                                                                                                      |  |  |

| V02.12            | 04 MAR<br>2002   | 04 MAR<br>2002 |        | - Document format updates.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| V02.13            | 22 JUL<br>2002   | 22 JUL<br>2002 |        | <ul> <li>Corrected TBPR register offset.</li> <li>Corrected Table 'Message Buffer Organization'.</li> <li>Corrected SLPRQ bit description.</li> <li>Corrected MSCAN Sleep Mode description.</li> <li>Updated WUPE bit description.</li> <li>Updated Simplified State Transitions figure.</li> <li>Updated Recovery from STOP or WAIT description and CPU vs. MSCAN Modes table.</li> </ul> |  |  |

| V02.14            | 18 SEP<br>2002   | 18 SEP<br>2002 |        | <ul> <li>- Added Initialization/Application information.</li> <li>- Replaced 'MCU' with 'CPU' in several places.</li> <li>- Cleaned up Mode descriptions.</li> <li>- General cleanup.</li> </ul>                                                                                                                                                                                           |  |  |

| V02.15            | 15 JUL<br>2004   | 15 JUL<br>2004 |        | <ul><li>Corrected buffer read/write access definitions.</li><li>Corrected bit time equation.</li></ul>                                                                                                                                                                                                                                                                                     |  |  |

## **Table of Contents**

| Sect  | ion 1 Introduction                      |    |

|-------|-----------------------------------------|----|

| 1.1   | Overview                                | 11 |

| 1.2   | Features                                | 12 |

| Sect  | ion 2 External Signal Description       |    |

| 2.1   | Overview                                | 13 |

| 2.2   | Detailed Signal Description             | 13 |

| 2.2.1 | RXCAN — CAN Receiver Input Pin          | 13 |

| 2.2.2 | TXCAN — CAN Transmitter Output Pin      | 13 |

| 2.3   | CAN System                              | 13 |

| Sect  | ion 3 Memory Map/Register Definition    |    |

| 3.1   | Overview                                | 15 |

| 3.2   | Module Memory Map                       | 15 |

| 3.3   | Register Descriptions                   | 16 |

| 3.3.1 | Programmer's Model of Control Registers | 17 |

| 3.3.2 | Programmer's Model of Message Storage   | 38 |

| Sect  | ion 4 Functional Description            |    |

| 4.1   | General                                 | 15 |

| 4.2   | Message Storage                         | 15 |

| 4.2.1 | Message Transmit Background             | 16 |

| 4.2.2 | Transmit Structures                     | 16 |

| 4.2.3 | Receive Structures                      | 17 |

| 4.3   | Identifier Acceptance Filter            | 18 |

| 4.3.1 | Protocol Violation Protection           | 52 |

| 4.3.2 | Clock System                            | 52 |

| 4.4   | Timer Link                              | 55 |

| 4.5   | Modes of Operation                      | 55 |

| 4.5.1 | Normal Modes                            | 55 |

| 4.5.2 | Special Modes                           | 55 |

| 4.5.3 | Emulation Modes                         | 55 |

| 4.5.4 | Listen-Only Mode                        | 55 |

#### **MSCAN Block Guide V02.15**

| 4.5.5 | Security Modes56                             |

|-------|----------------------------------------------|

| 4.6   | Low Power Options56                          |

| 4.6.1 | CPU Run Mode                                 |

| 4.6.2 | CPU Wait Mode                                |

| 4.6.3 | CPU Stop Mode                                |

| 4.6.4 | MSCAN Sleep Mode                             |

| 4.6.5 | MSCAN Initialization Mode                    |

| 4.6.6 | MSCAN Power Down Mode60                      |

| 4.6.7 | Programmable Wake-Up Function                |

| 4.7   | Reset Initialization61                       |

| 4.8   | General61                                    |

| 4.9   | Description of Interrupt Operation           |

| 4.9.1 | Transmit Interrupt62                         |

| 4.9.2 | Receive Interrupt                            |

| 4.9.3 | Wake-Up Interrupt                            |

| 4.9.4 | Error Interrupt62                            |

| 4.10  | Interrupt Acknowledge                        |

| 4.11  | Recovery from STOP or WAIT                   |

| Secti | ion 5 Initialization/Application Information |

| 5 1   | MSCAN initialization 63                      |

## **List of Figures**

| Figure 1-1  | MSCAN Block Diagram                                    | 11 |

|-------------|--------------------------------------------------------|----|

| Figure 2-1  | The CAN System                                         | 14 |

| Figure 3-1  | MSCAN Control 0 Register (CANCTL0)                     | 17 |

| Figure 3-2  | MSCAN Control 1 Register (CANCTL1)                     | 20 |

| Figure 3-3  | MSCAN Bus Timing Register 0 (CANBTR0)                  | 21 |

| Figure 3-4  | MSCAN Bus Timing Register 1 (CANBTR1)                  | 22 |

| Figure 3-5  | MSCAN Receiver Flag Register (CANRFLG)                 | 24 |

| Figure 3-6  | MSCAN Receiver Interrupt Enable Register (CANRIER)     | 26 |

| Figure 3-7  | MSCAN Transmitter Flag Register (CANTFLG)              | 28 |

| Figure 3-8  | MSCAN Transmitter Interrupt Enable Register (CANTIER)  | 29 |

| Figure 3-9  | MSCAN Transmitter Message Abort Request (CANTARQ)      | 29 |

| Figure 3-10 | MSCAN Transmitter Message Abort Control (CANTAAK)      | 30 |

| Figure 3-11 | MSCAN Transmitter Flag Register (CANTBSEL)             | 31 |

| Figure 3-12 | MSCAN Identifier Acceptance Control Register (CANIDAC) | 32 |

| Figure 3-13 | Reserved Registers                                     | 33 |

| Figure 3-14 | MSCAN Receive Error Counter Register (CANRXERR)        | 34 |

| Figure 3-15 | MSCAN Transmit Error Counter Register (CANTXERR)       | 34 |

| Figure 3-16 | MSCAN Identifier Acceptance Registers (1st Bank)       | 35 |

| Figure 3-17 | MSCAN Identifier Acceptance Registers (2nd Bank)       | 36 |

| Figure 3-18 | MSCAN Identifier Mask Registers (1st Bank)             | 37 |

| Figure 3-19 | MSCAN Identifier Mask Registers (2nd Bank)             | 37 |

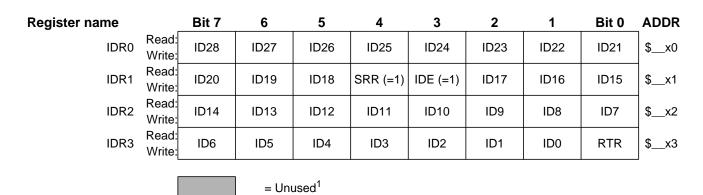

| Figure 3-20 | Receive / Transmit Message Buffer Extended Identifier  | 39 |

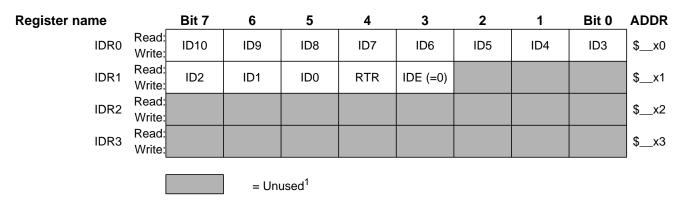

| Figure 3-21 | Standard Identifier Mapping                            | 40 |

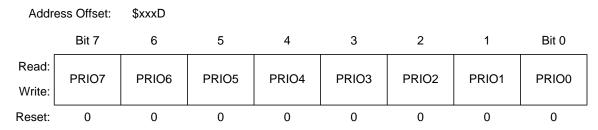

| Figure 3-22 | Transmit Buffer Priority Register (TBPR)               | 43 |

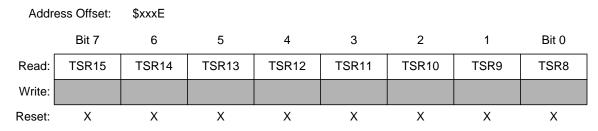

| Figure 3-23 | Time Stamp Register (TSRH - High Byte)                 | 43 |

| Figure 3-24 | Time Stamp Register (TSRL - Low Byte)                  | 44 |

| Figure 4-1  | User Model for Message Buffer Organization             | 45 |

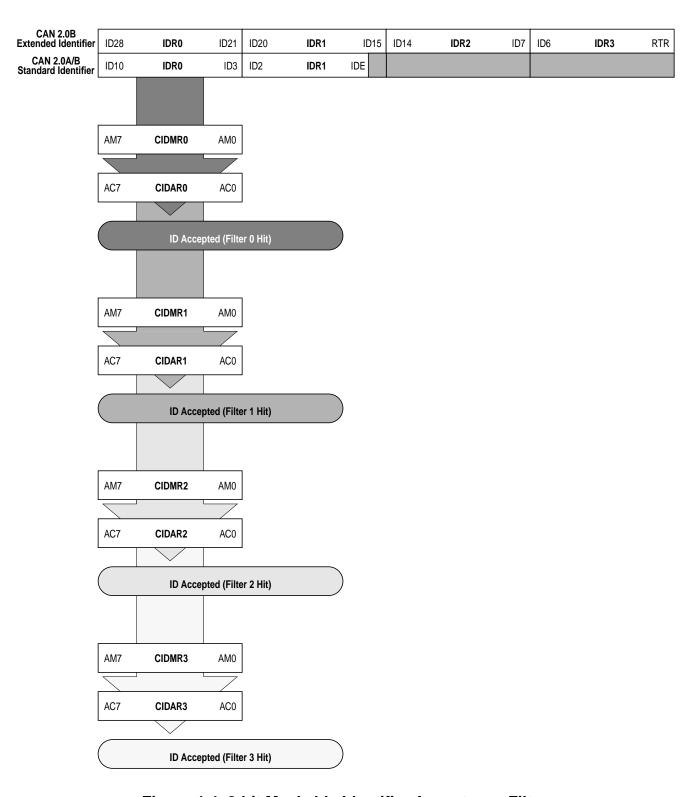

| Figure 4-2  | 32-bit Maskable Identifier Acceptance Filter           | 50 |

| Figure 4-3  | 16-bit Maskable Identifier Acceptance Filters          | 50 |

| Figure 4-4  | 8-bit Maskable Identifier Acceptance Filters           | 51 |

| Figure 4-5  | MSCAN Clocking Scheme                                  | 52 |

| Figure 4-6  | Segments within the Bit Time                           | 54 |

| Figure 4-7  | Sleep Request / Acknowledge Cycle                      | 57 |

#### **MSCAN Block Guide V02.15**

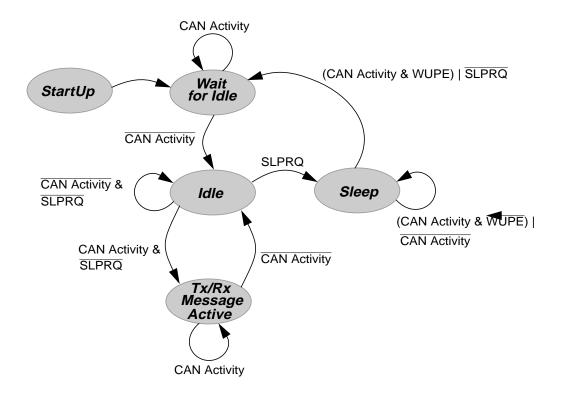

| Figure 4-8 | Simplified State Transitions for Entering/Leaving Sleep Mode | . 59 |

|------------|--------------------------------------------------------------|------|

| Figure 4-9 | Initialization Request/Acknowledge Cycle                     | . 60 |

6

## **List of Tables**

| Table 3-1  | MSCAN Register Organization                      | . 15 |

|------------|--------------------------------------------------|------|

| Table 3-2  | Module Memory Map                                | . 15 |

| Table 3-3  | Synchronization Jump Width                       | . 22 |

| Table 3-4  | Baud Rate Prescaler                              | . 22 |

| Table 3-5  | Time Segment 2 Values                            | . 23 |

| Table 3-6  | Time Segment 1 Values                            | . 24 |

| Table 3-7  | Identifier Acceptance Mode Settings              | . 32 |

| Table 3-8  | Identifier Acceptance Hit Indication             | . 33 |

| Table 3-9  | Message Buffer Organization                      | . 39 |

| Table 3-10 | Data length codes                                | . 42 |

| Table 4-1  | Time Segment Syntax                              | . 54 |

| Table 4-2  | CAN Standard Compliant Bit Time Segment Settings | . 55 |

| Table 4-3  | CPU vs. MSCAN Operating Modes                    | . 56 |

| Table 4-4  | CRG Interrupt Vectors                            | . 61 |

## **Preface**

## **Terminology**

| Acronyms and Abbreviations |                              |  |  |  |

|----------------------------|------------------------------|--|--|--|

| ACK                        | Acknowledge                  |  |  |  |

| CAN                        | Controller Area Network      |  |  |  |

| CRC                        | Cyclic Redundancy Code       |  |  |  |

| EOF                        | End of Frame                 |  |  |  |

| FIFO                       | First-In-First-Out Memory    |  |  |  |

| IFS                        | Inter-Frame Sequence         |  |  |  |

| MSCAN                      | Motorola Scalable CAN Module |  |  |  |

| SOF                        | Start of Frame               |  |  |  |

## **Section 1 Introduction**

#### 1.1 Overview

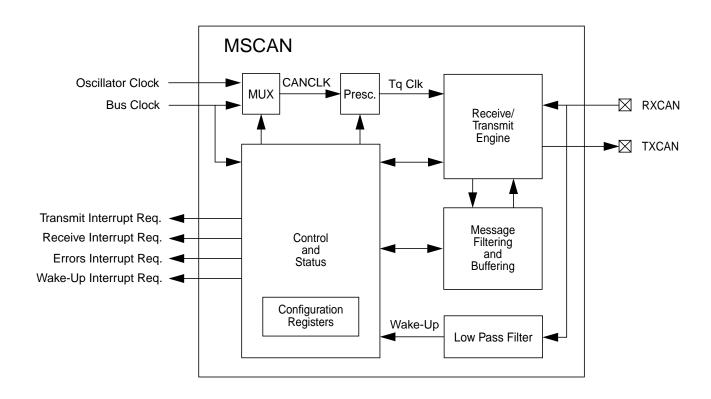

The Motorola Scalable Controller Area Network (MSCAN) definition is based on the MSCAN12 definition which is the specific implementation of the Motorola Scalable CAN concept targeted for the Motorola MC68HC12 Microcontroller Family.

The module is a communication controller implementing the CAN 2.0 A/B protocol as defined in the BOSCH specification dated September 1991. For users to fully understand the MSCAN specification, it is recommended that the Bosch specification be read first to familiarize the reader with the terms and concepts contained within this document.

The CAN protocol was primarily, but not only, designed to be used as a vehicle serial data bus, meeting the specific requirements of this field: real-time processing, reliable operation in the EMI environment of a vehicle, cost-effectiveness and required bandwidth.

MSCAN utilizes an advanced buffer arrangement resulting in a predictable real-time behavior and simplifies the application software.

Figure 1-1 MSCAN Block Diagram

### 1.2 Features

The basic features of the MSCAN are as follows:

- Implementation of the CAN protocol Version 2.0A/B

- Standard and extended data frames

- 0 8 bytes data length

- Programmable bit rate up to 1 Mbps<sup>1</sup>

- Support for remote frames

- 5 receive buffers with FIFO storage scheme

- 3 transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full size extended identifier filters (two 32-bit) or four 16-bit filters or eight 8-bit filters

- Programmable wake-up functionality with integrated low-pass filter

- Programmable loop back mode supports self-test operation

- Programmable listen-only mode for monitoring of CAN bus

- Separate signalling and interrupt capabilities for all CAN receiver and transmitter error states (Warning, Error Passive, Bus-Off)

- Programmable MSCAN clock source either Bus Clock or Oscillator Clock

- Internal timer for time-stamping of received and transmitted messages

- Three low power modes: Sleep, Power Down and MSCAN Enable

- Global initialization of configuration registers

#### NOTES:

1. Depending on the actual bit timing and the clock jitter of the PLL.

(M) MOTOROLA

## **Section 2 External Signal Description**

#### 2.1 Overview

This section lists and describes the signals that connect off chip.

## 2.2 Detailed Signal Description

The MSCAN uses two external pins.

### 2.2.1 RXCAN — CAN Receiver Input Pin

RXCAN is the MSCAN receiver input pin.

## 2.2.2 TXCAN — CAN Transmitter Output Pin

TXCAN is the MSCAN transmitter output pin. The TXCAN output pin represents the logic level on the CAN bus:

0 = Dominant state

1 =Recessive state

## 2.3 CAN System

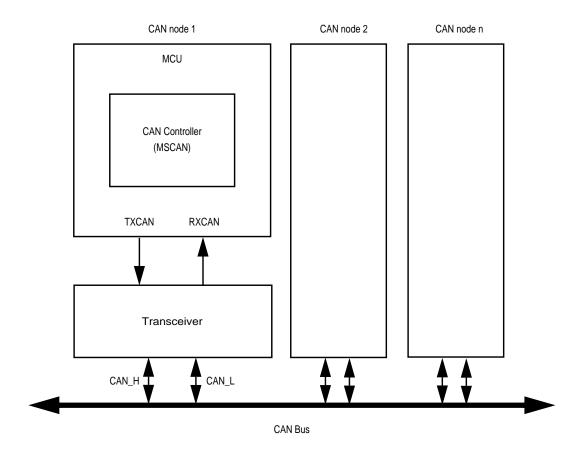

A typical CAN system with MSCAN is shown in **Figure 2-1**. Each CAN station is connected physically to the CAN bus lines through a transceiver chip. The transceiver is capable of driving the large current needed for the CAN bus and has current protection against defected CAN or defected stations.

Figure 2-1 The CAN System

## **Section 3 Memory Map/Register Definition**

#### 3.1 Overview

This section provides a detailed description of all registers accessible in the MSCAN.

## 3.2 Module Memory Map

**Table 3-1** and **Table 3-2** give an overview on all registers and their individual bits in the MSCAN memory map. The *register address* results from the addition of *base address* and *address offset*. The *base address* is determined at the MCU level. The *address offset* is defined at the module level.

The MSCAN occupies 64 bytes in the memory space. The base address of the MSCAN module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset.

| Address<br>Offset |                   |

|-------------------|-------------------|

| \$00              | CONTROL REGISTERS |

| \$0B              | 12 BYTES          |

| \$0C              | RESERVED          |

| \$0D              | 2 BYTES           |

| \$0E              | ERROR COUNTERS    |

| \$0F              | 2 BYTES           |

| \$10              | IDENTIFIER FILTER |

| \$1F              | 16 BYTES          |

| \$20              | RECEIVE BUFFER    |

| \$2F              | 16 BYTES (Window) |

| \$30              | TRANSMIT BUFFER   |

| \$3F              | 16 BYTES (Window) |

**Table 3-1 MSCAN Register Organization**

**Table 3-1** shows the individual registers associated with the MSCAN and their relative offset from the base address. The detailed register descriptions follow in the order they appear in the register map (see **Table 3-2**).

**Table 3-2 Module Memory Map**

| Address | Use                                   | Access           |

|---------|---------------------------------------|------------------|

| \$00    | MSCAN Control Register 0 (CANCTL0)    | R/W <sup>1</sup> |

| \$01    | MSCAN Control Register 1 (CANCTL1)    | R/W <sup>1</sup> |

| \$02    | MSCAN Bus Timing Register 0 (CANBTR0) | R/W              |

| \$03    | MSCAN Bus Timing Register 1 (CANBTR1) | R/W              |

| \$04          | MSCAN Receiver Flag Register (CANRFLG)                 | R/W <sup>1</sup>  |

|---------------|--------------------------------------------------------|-------------------|

| \$05          | MSCAN Receiver Interrupt Enable Register (CANRIER)     | R/W               |

| \$06          | MSCAN Transmitter Flag Register (CANTFLG)              | R/W <sup>1</sup>  |

| \$07          | MSCAN Transmitter Interrupt Enable Register (CANTIER)  | R/W <sup>1</sup>  |

| \$08          | MSCAN Transmitter Message Abort Control (CANTARQ)      | R/W <sup>1</sup>  |

| \$09          | MSCAN Transmitter Message Abort Control (CANTAAK)      | R                 |

| \$0A          | MSCAN Transmit Buffer Selection (CANTBSEL)             | R/W <sup>1</sup>  |

| \$0B          | MSCAN Identifier Acceptance Control Register (CANIDAC) | R/W <sup>1</sup>  |

| \$0C<br>-\$0D | RESERVED                                               |                   |

| \$0E          | MSCAN Receive Error Counter Register (CANRXERR)        | R                 |

| \$0F          | MSCAN Transmit Error Counter Register (CANTXERR)       | R                 |

| \$10          | MSCAN Identifier Acceptance Register 0 (CANIDAR0)      | R/W               |

| \$11          | MSCAN Identifier Acceptance Register 1 (CANIDAR1)      | R/W               |

| \$12          | MSCAN Identifier Acceptance Register 2 (CANIDAR2)      | R/W               |

| \$13          | MSCAN Identifier Acceptance Register 3 (CANIDAR3)      | R/W               |

| \$14          | MSCAN Identifier Mask Register 0 (CANIDMR0)            | R/W               |

| \$15          | MSCAN Identifier Mask Register 1 (CANIDMR1)            | R/W               |

| \$16          | MSCAN Identifier Mask Register 2 (CANIDMR2)            | R/W               |

| \$17          | MSCAN Identifier Mask Register 3 (CANIDMR3)            | R/W               |

| \$18          | MSCAN Identifier Acceptance Register 4 (CANIDAR4)      | R/W               |

| \$19          | MSCAN Identifier Acceptance Register 5 (CANIDAR5)      | R/W               |

| \$1A          | MSCAN Identifier Acceptance Register 6 (CANIDAR6)      | R/W               |

| \$1B          | MSCAN Identifier Acceptance Register 7 (CANIDAR7)      | R/W               |

| \$1C          | MSCAN Identifier Mask Register 4 (CANIDMR4)            | R/W               |

| \$1D          | MSCAN Identifier Mask Register 5 (CANIDMR5)            | R/W               |

| \$1E          | MSCAN Identifier 6 Mask Register 6 (CANIDMR6)          | R/W               |

| \$1F          | MSCAN Identifier Mask Register 7 (CANIDMR7)            | R/W               |

| \$20<br>-\$2F | Foreground Receive Buffer (CANRXFG)                    | R <sup>2</sup>    |

| \$30<br>-\$3F | Foreground Transmit Buffer (CANTXFG)                   | R <sup>2</sup> /W |

|               |                                                        |                   |

#### NOTES:

- 1. Refer to detailed register description for write access restrictions on per bit basis.

- Reserved bits and unused bits within the TX- and RX-Buffers (CANTXFG, CAN-RXFG) will be read as "X", because of RAM based implementation.

## 3.3 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

MOTOROLA

### 3.3.1 Programmer's Model of Control Registers

The programmer's model is laid out for maximum simplicity and efficiency. **Table 3-2** provides an overview of the control registers for the MSCAN.

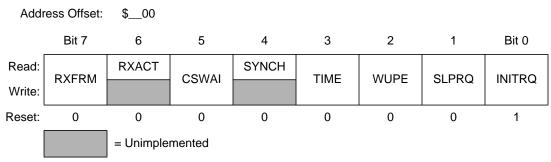

#### 3.3.1.1 MSCAN Control 0 Register (CANCTL0)

The CANCTL0 register provides for various control of the MSCAN module as described below.

Figure 3-1 MSCAN Control 0 Register (CANCTL0)

**NOTE:** The CANCTLO register, except the WUPE, INITRQ and SLPRQ bits, is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

Read: Anytime

Write: Anytime when out of Initialization Mode; exceptions are read-only bits RXACT and SYNCH, bit RXFRM which is set by the module only and bit INITRQ which is also writable in Initialization Mode.

#### RXFRM — Received Frame Flag

This bit is read and clear only. It is set when a receiver has received a valid message correctly, independently of the filter configuration. Once set, it remains set until cleared by software or reset. Clearing is done by writing a '1' to the bit. A write '0' is ignored. This bit is not valid in loop back mode.

- 1 = A valid message was received since last clearing of this flag

- 0 = No valid message was received since last clearing this flag.

**NOTE:** The MSCAN must be in Normal Mode for this bit to become set.

#### RXACT — Receiver Active Status

This read-only flag indicates the MSCAN is receiving a message. The flag is controlled by the receiver front end. This bit is not valid in loop back mode.

- 1 = MSCAN is receiving a message (including when arbitration is lost)<sup>1</sup>

- 0 = MSCAN is transmitting or idle<sup>1</sup>.

#### **MSCAN Block Guide V02.15**

#### CSWAI — CAN Stops in Wait Mode

Enabling this bit allows for lower power consumption in Wait Mode by disabling all the clocks at the bus interface to the MSCAN module.

- 1 = The module ceases to be clocked during Wait Mode.

- 0 = The module is not affected during Wait Mode.

NOTE: In order to protect from accidentally violating the CAN protocol the TXCAN pin is immediately forced to a recessive state when the CPU enters Wait (CSWAI=1) or Stop Mode (see 4.6.2 CPU Wait Mode and 4.6.3 CPU Stop Mode)

#### SYNCH — Synchronized Status

This read-only flag indicates whether the MSCAN is synchronized to the CAN bus and, as such, can participate in the communication process. It is set and cleared by the MSCAN.

- 1 = MSCAN is synchronized to the CAN bus.

- 0 = MSCAN is not synchronized to the CAN bus.

#### TIME - Timer Enable

This bit activates an internal 16-bit wide free running timer which is clocked by the bit clock. If the timer is enabled, a 16-bit time stamp will be assigned to each transmitted/received message within the active TX/RX buffer. As soon as a message is acknowledged on the CAN bus, the time stamp will be written to the highest bytes (\$\_E, \$\_F) in the appropriate buffer 3.3.2 Programmer's Model of

**Message Storage**. The internal timer is reset (all bits set to "0") when Initialization Mode is active.

- 1 = Enable internal MSCAN timer.

- 0 = Disable internal MSCAN timer.

#### WUPE — Wake-Up Enable

This configuration bit allows the MSCAN to restart from Sleep Mode when traffic on CAN is detected (see 4.6.4 MSCAN Sleep Mode).

- 1 = Wake-Up enabled—The MSCAN is able to restart.

- 0 = Wake-Up disabled The MSCAN ignores traffic on CAN.

#### **NOTE:** The CPU has to make sure that the WUPE register and the WUPIE Wake-Up interrupt enable register 3.3.1.6 MSCAN Receiver Interrupt Enable Register (CANRIER) is enabled, if the recovery mechanism from STOP or WAIT is required.

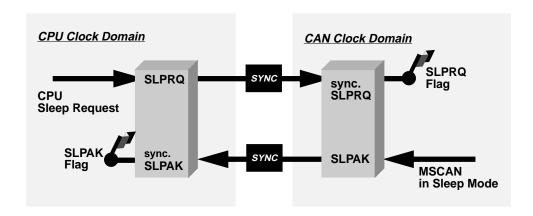

#### SLPRQ — Sleep Mode Request

This bit requests the MSCAN to enter Sleep Mode, which is an internal power saving mode (see 4.6.4 **MSCAN Sleep Mode**). The Sleep Mode request is serviced when the CAN bus is idle, i.e. the module is not receiving a message and all transmit buffers are empty. The module indicates entry to Sleep Mode by setting SLPAK=1 (3.3.1.2 MSCAN Control 1 Register (CANCTL1)). Sleep Mode will be active until SLPRQ is cleared by the CPU or, depending on the setting of WUPE bit, the MSCAN detects bus activity on CAN and clears the SLPRQ itself.

#### NOTES:

1. See the Bosch CAN 2.0A/B protocol specification dated September 1991 for a detailed definition of transmitter and receiver states.

- 1 = Sleep Mode Request The MSCAN enters Sleep Mode when CAN bus idle.

- 0 = Running The MSCAN functions normally.

**NOTE:** The CPU cannot clear the SLPRQ bit before the MSCAN has entered Sleep Mode (SLPRQ=1 and SLPAK=1)

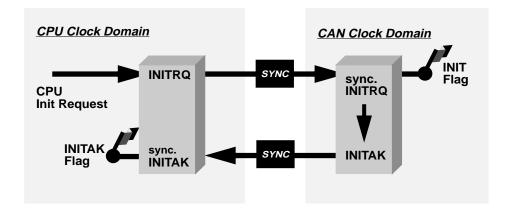

INITRQ — Initialization Mode Request

When this bit is set by the CPU, the MSCAN skips to Initialization Mode (see **4.6.5 MSCAN Initialization Mode**). Any ongoing transmission or reception is aborted and synchronization to the bus is lost. The module indicates entry to Initialization Mode by setting INITAK=1 (**3.3.1.2 MSCAN Control 1 Register (CANCTL1)**).

The following registers enter their hard reset state and restore their default values: CANCTL0<sup>1</sup>, CANRFLG<sup>2</sup>, CANRIER<sup>3</sup>, CANTFLG, CANTIER, CANTARQ, CANTAAK, CANTBSEL.

The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0-7, CANIDMR0-7 can only be written by the CPU when the MSCAN is in Initialization Mode (INITRQ=1 and INITAK=1). The values of the error counters are not affected by Initialization Mode.

When this bit is cleared by the CPU, the MSCAN restarts and then tries to synchronize to the CAN bus. If the MSCAN is not in Bus-Off state, it synchronizes after 11 consecutive recessive bits on the bus; if the MSCAN is in Bus-Off state it continues to wait for 128 occurrences of 11 consecutive recessive bits.

Writing to other bits in CANCTLO, CANRFLG, CANRIER, CANTFLG or CANTIER must only be done after Initialization Mode is left, which is INITRQ=0 and INITAK=0.

- 1 = MSCAN in Initialization Mode.

- 0 = Normal operation.

**NOTE:** The CPU cannot clear the INITRQ bit before the MSCAN has entered Initialization Mode (INITRQ=1 and INITAK=1)

**NOTE:** In order to protect from accidentally violating the CAN protocol the TXCAN pin is immediately forced to a recessive state when the Initialization Mode is requested by the CPU. Thus the recommended procedure is to bring the MSCAN into Sleep Mode (SLPRQ=1 and SLPAK=1) before.

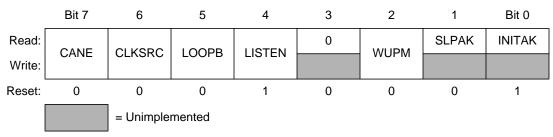

#### 3.3.1.2 MSCAN Control 1 Register (CANCTL1)

The CANCTL1 register provides for various control and handshake status information of the MSCAN module as described below.

Address Offset: \$\_\_01

#### NOTES:

- 1. Except the WUPE, INITRQ and SLPRQ bits

- 2. The TSTAT1, TSTAT0 bits are not affected by Initialization Mode

- 3. The RSTAT1, RSTAT0 bits are not affected by Initialization Mode

Figure 3-2 MSCAN Control 1 Register (CANCTL1)

Read: Anytime

Write: Anytime when INITRQ=1 <u>and</u> INITAK=1, except CANE which is write once in normal and anytime in special system operation modes when the MSCAN is in Initialization Mode (INITRQ=1 and INITAK=1).

CANE — MSCAN Enable

- 1 = The MSCAN module is enabled.

- 0 =The MSCAN module is disabled.

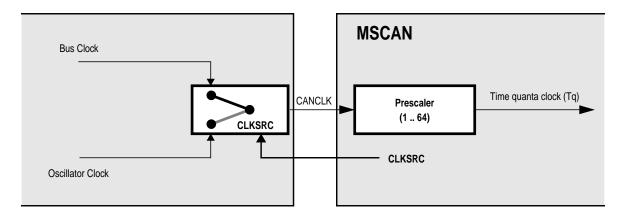

#### CLKSRC — MSCAN Clock Source

This bit defines the clock source for the MSCAN module (only for systems with a clock generation module; **4.3.2 Clock System** and **Figure 4-5**).

- 1 = The MSCAN clock source is the Bus Clock.

- 0 = The MSCAN clock source is the Oscillator Clock.

#### LOOPB — Loop Back Self Test Mode

When this bit is set, the MSCAN performs an internal loop back which can be used for self test operation. The bit stream output of the transmitter is fed back to the receiver internally. The RXCAN input pin is ignored and the TXCAN output goes to the recessive state (logic '1'). The MSCAN behaves as it does normally when transmitting and treats its own transmitted message as a message received from a remote node. In this state, the MSCAN ignores the bit sent during the ACK slot in the CAN frame Acknowledge field to ensure proper reception of its own message. Both transmit and receive interrupts are generated.

- 1 = Loop Back Self Test enabled

- 0 = Loop Back Self Test disabled

#### LISTEN — Listen Only Mode

This bit configures the MSCAN as a bus monitor. When the bit is set, all valid CAN messages with matching ID are received, but no acknowledgement or error frames are sent out **4.5.4 Listen-Only Mode**. In addition the error counters are frozen.

Listen Only Mode supports applications which require "hot plugging" or throughput analysis. The MSCAN is unable to transmit any messages, when Listen Only Mode is active.

- 1 = Listen Only Mode activated

- 0 = Normal operation

#### WUPM — Wake-Up Mode

This bit defines whether the integrated low-pass filter is applied to protect the MSCAN from spurious wake-up **4.6.4 MSCAN Sleep Mode**.

- 1 = MSCAN wakes-up the CPU only in case of a dominant pulse on the bus which has a length of  $T_{wup}$  and WUPE=1 in CANCTL0 (see 3.3.1.1 MSCAN Control 0 Register (CANCTL0)).

- 0 = MSCAN wakes-up the CPU after any recessive to dominant edge on the CAN bus and WUPE=1 in CANCTL0.

#### SLPAK — Sleep Mode Acknowledge

This flag indicates whether the MSCAN module has entered Sleep Mode **4.6.4 MSCAN Sleep Mode**. It is used as a handshake flag for the SLPRQ Sleep Mode request. Sleep Mode is active when SLPRQ=1 and SLPAK=1. Depending on the setting of the WUPE bit the MSCAN will clear the flag if it detects bus activity on CAN while in Sleep Mode.

- 1 = Sleep Mode Active The MSCAN has entered Sleep Mode.

- 0 = Running The MSCAN operates normally.

#### INITAK — Initialization Mode Acknowledge

This flag indicates whether the MSCAN module is in Initialization Mode **4.6.5 MSCAN Initialization Mode**. It is used as a handshake flag for the INITRQ Initialization Mode request. Initialization Mode is active when INITRQ=1 and INITAK=1.

The registers CANCTL1, CANBTR0, CANBTR1, CANIDAC, CANIDAR0-7, CANIDMR0-7 can only be written by the CPU when the MSCAN is in Initialization Mode.

- 1 = Initialization Mode Active The MSCAN has entered Initialization Mode.

- 0 = Running The MSCAN operates normally.

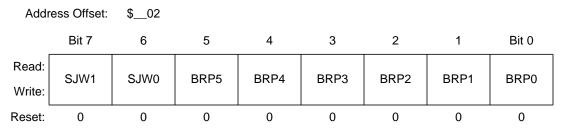

### 3.3.1.3 MSCAN Bus Timing Register 0 (CANBTR0)

The CANBTR0 register provides for various bus timing control of the MSCAN module as described below.

Figure 3-3 MSCAN Bus Timing Register 0 (CANBTR0)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ=1 and INITAK=1)

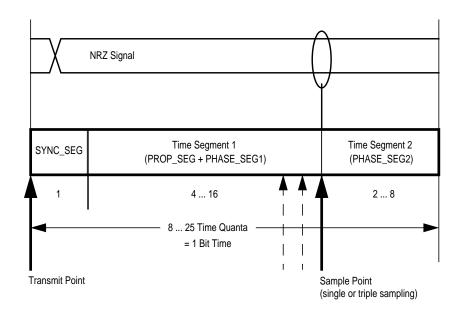

SJW1, SJW0 — Synchronization Jump Width

#### **MSCAN Block Guide V02.15**

The synchronization jump width defines the maximum number of time quanta (Tq) clock cycles a bit can be shortened or lengthened to achieve resynchronization to data transitions on the bus (see **Table 3-3**).

**Table 3-3 Synchronization Jump Width**

| SJW1 | SJW0 | Synchronization jump width |  |  |

|------|------|----------------------------|--|--|

| 0    | 0    | 1 Tq clock cycle           |  |  |

| 0    | 1    | 2 Tq clock cycles          |  |  |

| 1    | 0    | 3 Tq clock cycles          |  |  |

| 1    | 1    | 4 Tq clock cycles          |  |  |

#### BRP[5-0] — Baud Rate Prescaler

These bits determine the time quanta (Tq) clock which is used to build up the individual bit timing, as shown in **Table 3-4**.

Table 3-4 Baud Rate Prescaler

| BRP5 | BRP4 | BRP3 | BRP2 | BRP1 | BRP0 | Prescaler<br>value (P) |

|------|------|------|------|------|------|------------------------|

| 0    | 0    | 0    | 0    | 0    | 0    | 1                      |

| 0    | 0    | 0    | 0    | 0    | 1    | 2                      |

| 0    | 0    | 0    | 0    | 1    | 0    | 3                      |

| 0    | 0    | 0    | 0    | 1    | 1    | 4                      |

| :    | :    | :    | :    | :    | :    | :                      |

| 1    | 1    | 1    | 1    | 1    | 0    | 63                     |

| 1    | 1    | 1    | 1    | 1    | 1    | 64                     |

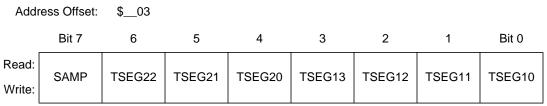

## 3.3.1.4 MSCAN Bus Timing Register 1 (CANBTR1)

The CANBTR1 register provides for various bus timing control of the MSCAN module as described below.

Figure 3-4 MSCAN Bus Timing Register 1 (CANBTR1)

Reset: 0 0 0 0 0 0 0 0

Figure 3-4 MSCAN Bus Timing Register 1 (CANBTR1)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ=1 and INITAK=1)

#### SAMP — Sampling

This bit determines the number of samples of the serial bus to be taken per bit time. If set, three samples per bit are taken; the regular one (sample point) and two preceding samples using a majority rule. For higher bit rates, it is recommended that SAMP be cleared which means that only one sample is taken per bit.

- 1 =Three samples per bit $^1$ .

- 0 =One sample per bit.

#### TSEG22 – TSEG20 — Time Segment 2

Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see **Figure 4-6 Segments within the Bit Time**).

Time segment 2 (TSEG2) values are programmable as shown in **Table 3-5**.

TSEG22 TSEG21 TSEG20 **Time segment 2** 1 Tq clock cycle<sup>1</sup> 2 Tq clock cycles 0 0 1 1 0 7 Tq clock cycles 1 8 Tq clock cycles 1 1 1

**Table 3-5 Time Segment 2 Values**

#### NOTES:

#### TSEG13 – TSEG10 — Time Segment 1

Time segments within the bit time fix the number of clock cycles per bit time and the location of the sample point (see **Figure 4-6 Segments within the Bit Time**).

Time segment 1 (TSEG1) values are programmable as shown in **Table 3-6**.

#### NOTES:

1. In this case, PHASE\_SEG1 must be at least 2 Time Quanta.

This setting is not valid. Please refer to Table 4-2 CAN Standard Compliant Bit Time Segment Settings for valid settings.

|        |        |        | _      |                                |

|--------|--------|--------|--------|--------------------------------|

| TSEG13 | TSEG12 | TSEG11 | TSEG10 | Time segment 1                 |

| 0      | 0      | 0      | 0      | 1 Tq clock cycle <sup>1</sup>  |

| 0      | 0      | 0      | 1      | 2 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 0      | 3 Tq clock cycles <sup>1</sup> |

| 0      | 0      | 1      | 1      | 4 Tq clock cycles              |

|        |        |        |        |                                |

| 1      | 1      | 1      | 0      | 15 Tq clock cycles             |

| 1      | 1      | 1      | 1      | 16 Tq clock cycles             |

**Table 3-6 Time Segment 1 Values**

#### NOTES:

The bit time is determined by the oscillator frequency, the baud rate prescaler, and the number of time quanta (Tq) clock cycles per bit (as shown in **Table 3-5** and **Table 3-6** above).

Bit Time=

$$\frac{(Prescaler\ value)}{f_{CANCLK}} \bullet (1 + TimeSegment1 + TimeSegment2)$$

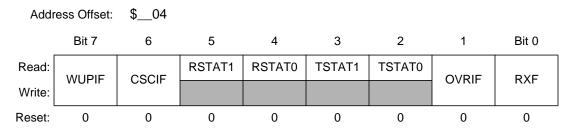

#### 3.3.1.5 MSCAN Receiver Flag Register (CANRFLG)

A flag can only be cleared when the condition which caused the setting is no longer valid and can only be cleared by software (writing a '1' to the corresponding bit position). Every flag has an associated interrupt enable bit in the CANRIER register.

Figure 3-5 MSCAN Receiver Flag Register (CANRFLG)

This setting is not valid. Please refer to Table 4-2 CAN Standard Compliant Bit Time Segment Settings for valid settings.

**NOTE:** The CANRFLG register is held in the reset state<sup>1</sup> when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

Read: Anytime

Write: Anytime when out of Initialization Mode, except RSTAT[1:0] and TSTAT[1:0] flags which are read-only; write of '1' clears flag; write of '0' ignored

#### WUPIF — Wake-Up Interrupt Flag

If the MSCAN detects bus activity while in Sleep Mode **4.6.4 MSCAN Sleep Mode** and the WUPE=1 in CANTCTL0 (see **3.3.1.1 MSCAN Control 0 Register (CANCTL0)**), it will set the WUPIF flag. If not masked, a Wake-Up interrupt is pending while this flag is set.

- 1 = MSCAN detected activity on the bus and requested wake-up.

- 0 = No wake-up activity observed while in Sleep Mode.

#### CSCIF — CAN Status Change Interrupt Flag

This flag is set when the MSCAN changes its current bus status due to the actual value of the Transmit Error Counter (TEC) and the Receive Error Counter (REC). An additional 4-bit (RSTAT[1:0], TSTAT[1:0]) status register, which is split into separate sections for TEC/REC, informs the system on the actual bus status 3.3.1.6 MSCAN Receiver Interrupt Enable Register (CANRIER). If not masked, an Error interrupt is pending while this flag is set. CSCIF provides a blocking interrupt. That guarantees that the Receiver / Transmitter status bits (RSTAT/TSTAT) are only updated when no CAN Status Change interrupt is pending. If the TECs/RECs change their current value after the CSCIF is asserted and therefore would cause an additional state change in the RSTAT/TSTAT bits, these bits keep their old state bits until the current CSCIF interrupt is cleared again.

- 1 = MSCAN changed current bus status.

- 0 = No change in bus status occurred since last interrupt.

#### RSTAT1, RSTAT0 — Receiver Status Bits

The values of the error counters control the actual bus status of the MSCAN. As soon as the Status Change Interrupt Flag (CSCIF) is set these bits indicate the appropriate receiver related bus status of the MSCAN. The coding for the bits RSTAT1, RSTAT0 is:

00 = RxOK:  $0 \le Receive Error Counter \le 96$ 01 = RxWRN:  $96 < Receive Error Counter \le 127$

10 = RxERR: 127 < Receive Error Counter

$11 = Bus-Off^2$ : Transmit Error Counter > 255

#### TSTAT1, TSTAT0 — Transmitter Status Bits

The values of the Error Counters control the actual bus status of the MSCAN. As soon as the Status Change Interrupt Flag (CSCIF) is set these bits indicate the appropriate transmitter related bus status of the MSCAN. The coding for the bits TSTAT1, TSTAT0 is:

#### NOTES:

- 1. The RSTAT[1:0], TSTAT[1:0] bits are not affected by Initialization Mode

- 2. Redundant Information for the most critical bus status which is "CAN Bus-Off". This only occurs if the Tx Error Counter exceeds a number of 255 errors. CAN Bus-Off affects the receiver state. As soon as the transmitter leaves its Bus-Off state the receiver state skips to RxOK too. Refer also to TSTAT[1:0] coding.

#### **MSCAN Block Guide V02.15**

00 = TxOK:  $0 \le \text{Transmit Error Counter} \le 96$  01 = TxWRN:  $96 < \text{Transmit Error Counter} \le 127$  10 = TxERR:  $127 < \text{Transmit Error Counter} \le 255$ 11 = Bus-Off: Transmit Error Counter > 255

#### OVRIF — Overrun Interrupt Flag

This flag is set when a data overrun condition occurs. If not masked, an Error interrupt is pending while this flag is set.

- 1 = A data overrun detected.

- 0 =No data overrun condition.

#### RXF — Receive Buffer Full Flag

The RXF flag is set by the MSCAN when a new message is shifted in the receiver FIFO. This flag indicates whether the shifted buffer is loaded with a correctly received message (matching identifier, matching Cyclic Redundancy Code (CRC) and no other errors detected). After the CPU has read that message from the RxFG buffer in the receiver FIFO, the RXF flag must be cleared to release the buffer. A set RXF flag prohibits the shifting of the next FIFO entry into the foreground buffer (RxFG). If not masked, a Receive interrupt is pending while this flag is set.

- 1 = The receiver FIFO is not empty. A new message is available in the RxFG.

- 0 =No new message available within the RxFG.

**NOTE:** To ensure data integrity, do not read the receive buffer registers while the RXF flag is cleared.

For MCUs with dual CPUs, reading the receive buffer registers while the RXF flag is cleared may result in a CPU fault condition.

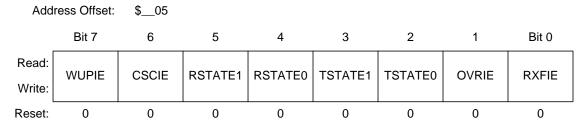

#### 3.3.1.6 MSCAN Receiver Interrupt Enable Register (CANRIER)

This register contains the interrupt enable bits for the interrupt flags described above.

Figure 3-6 MSCAN Receiver Interrupt Enable Register (CANRIER)

**NOTE:** The CANRIER register is held in the reset state<sup>1</sup> when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

#### NOTES:

1. The RSTATE[1:0], TSTATE[1:0] bits are not affected by Initialization Mode

Read: Anytime

Write: Anytime when out of Initialization Mode

WUPIE — Wake-Up Interrupt Enable

- 1 = A wake-up event causes a Wake-Up interrupt request.

- 0 = No interrupt request is generated from this event.

**NOTE:** The CPU has to make sure that the Wake-Up interrupt register and the WUPE register 3.3.1.1 MSCAN Control 0 Register (CANCTL0) is enabled, if the recovery mechanism from STOP or WAIT is required.

CSCIE — CAN Status Change Interrupt Enable

- 1 = A CAN Status Change event causes an error interrupt request.

- 0 = No interrupt request is generated from this event.

#### RSTATE1, RSTATE0— Receiver Status Change Enable

These RSTAT enable bits control the sensitivity level in which receiver state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level the RSTAT flags still indicate the actual receiver state and are only updated if no CSCIF interrupt is pending.

- 11 = generate CSCIF interrupt on all state changes

- 10 = generate CSCIF interrupt only if the receiver enters or leaves "RxErr" or "Bus-Off" state. Discard other receiver state changes for generating CSCIF interrupt.

- 01 = generate CSCIF interrupt only if the receiver enters or leaves "Bus-Off" state. Discard other receiver state changes for generating CSCIF interrupt.

- 00 = do not generate any CSCIF interrupt caused by receiver state changes.

#### TSTATE1, TSTATE0— Transmitter Status Change Enable

These TSTAT enable bits control the sensitivity level in which transmitter state changes are causing CSCIF interrupts. Independent of the chosen sensitivity level the TSTAT flags still indicate the actual transmitter state and are only updated if no CSCIF interrupt is pending.

- 11 = generate CSCIF interrupt on all state changes

- 10 = generate CSCIF interrupt only if the transmitter enters or leaves "TxErr" or "Bus-Off" state. Discard other transmitter state changes for generating CSCIF interrupt.

- 01 = generate CSCIF interrupt only if the transmitter enters or leaves "Bus-Off" state. Discard other transmitter state changes for generating CSCIF interrupt.

- 00 = do not generate any CSCIF interrupt caused by transmitter state changes.

OVRIE — Overrun Interrupt Enable

- 1 = An overrun event causes an error interrupt request.

- 0 = No interrupt request is generated from this event.

#### RXFIE — Receiver Full Interrupt Enable

#### NOTES:

1. Bus-Off state is only defined by the CAN standard for transmitters. Because the only possible state change for the transmitter from Bus-Off to TxOK also forces the receiver to skip its current state to RxOK, the coding of the RXSTAT[1:0] flags define an additional Bus-Off state for the receiver 3.3.1.5 MSCAN Receiver Flag Register (CANRFLG)

- 1 = A receive buffer full (successful message reception) event causes a receiver interrupt request.

- 0 = No interrupt request is generated from this event.

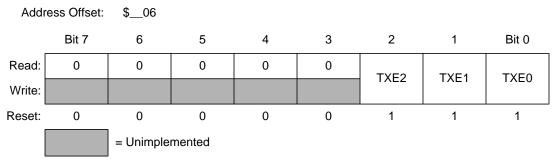

#### 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)

The Transmit Buffer Empty flags each have an associated interrupt enable bit in the CANTIER register.

Figure 3-7 MSCAN Transmitter Flag Register (CANTFLG)

**NOTE:** The CANTFLG register is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRO=0 and INITAK=0).

Read: Anytime

Write: Anytime for TXEx flags when not in Initialization Mode; write of '1' clears flag, write of '0' ignored

#### TXE2 - TXE0 —Transmitter Buffer Empty

This flag indicates that the associated transmit message buffer is empty, and thus not scheduled for transmission. The CPU must clear the flag after a message is set up in the transmit buffer and is due for transmission. The MSCAN sets the flag after the message is sent successfully. The flag is also set by the MSCAN when the transmission request is successfully aborted due to a pending abort request (see **3.3.1.9 MSCAN Transmitter Message Abort Control (CANTARQ)**). If not masked, a Transmit interrupt is pending while this flag is set.

Clearing a TXEx flag also clears the corresponding ABTAKx (see 3.3.1.10 MSCAN Transmitter Message Abort Control (CANTAAK)). When a TXEx flag is set, the corresponding ABTRQx bit is cleared (see 3.3.1.9 MSCAN Transmitter Message Abort Control (CANTARQ)).

When Listen-Mode is active (see **3.3.1.2 MSCAN Control 1 Register (CANCTL1)**) the TXEx flags cannot be cleared and no transmission is started.

Read and write accesses to the transmit buffer will be blocked, if the corresponding TXEx bit is cleared (TXEx='0') and the buffer is scheduled for transmission.

- 1 = The associated message buffer is empty (not scheduled).

- 0 =The associated message buffer is full (loaded with a message due for transmission).

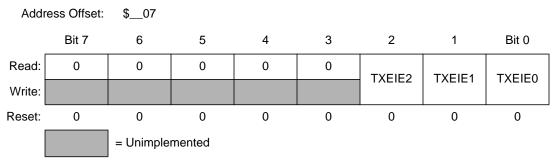

#### 3.3.1.8 MSCAN Transmitter Interrupt Enable Register (CANTIER)

This register contains the interrupt enable bits for the Transmit Buffer Empty interrupt flags.

Figure 3-8 MSCAN Transmitter Interrupt Enable Register (CANTIER)

**NOTE:** The CANTIER register is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

Read: Anytime

Write: Anytime when not in Initialization Mode

TXEIE2 - TXEIE0 — Transmitter Empty Interrupt Enable

- 1 = A transmitter empty (transmit buffer available for transmission) event causes a transmitter empty interrupt request.

- 0 = No interrupt request is generated from this event.

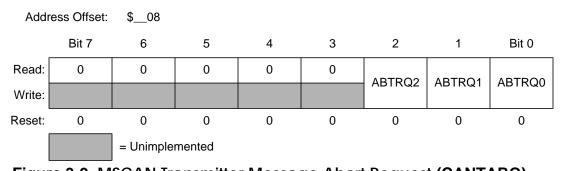

## 3.3.1.9 MSCAN Transmitter Message Abort Control (CANTARQ)

The CANTARQ register provides for abort request of queued messages as described below.

Figure 3-9 MSCAN Transmitter Message Abort Request (CANTARQ)

**NOTE:** The CANTARQ register is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

#### **MSCAN Block Guide V02.15**

Read: Anytime

Write: Anytime when not in Initialization Mode

#### ABTRQ2 - ABTRQ0 — Abort Request

The CPU sets the ABTRQx bit to request that a scheduled message buffer (TXEx=0) be aborted. The MSCAN grants the request if the message has not already started transmission, or if the transmission is not successful (lost arbitration or error). When a message is aborted, the associated TXE (see 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)) and Abort Acknowledge flags (ABTAK, see 3.3.1.10 MSCAN Transmitter Message Abort Control (CANTAAK)) are set and a transmit interrupt occurs if enabled. The CPU cannot reset ABTRQx. ABTRQx is reset whenever the associated TXE flag is set.

- 1 = Abort request pending.

- 0 = No abort request.

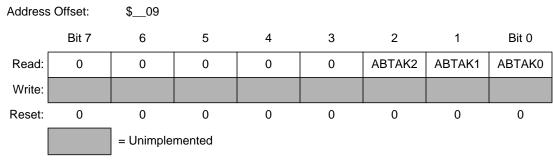

#### 3.3.1.10 MSCAN Transmitter Message Abort Control (CANTAAK)

The CANTAAK register indicates the successful abort of a queued message, if requested by the appropriate bits in the CANTARQ register

Figure 3-10 MSCAN Transmitter Message Abort Control (CANTAAK)

**NOTE:** The CANTAAK register is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1).

Read: Anytime

Write: Unimplemented for ABTAKx flags;

#### ABTAK2 - ABTAK0 — Abort Acknowledge

This flag acknowledges that a message was aborted due to a pending abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.

- 1 = The message was aborted.

- 0 = The message was not aborted.

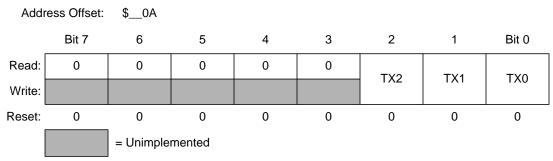

#### 3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL)

The CANTBSEL register allows the selection of the actual transmit message buffer, which will be then accessible in the CANTXFG register space (3.3.1 Programmer's Model of Control Registers).

Figure 3-11 MSCAN Transmitter Flag Register (CANTBSEL)

**NOTE:** The CANTBSEL register is held in the reset state when the Initialization Mode is active (INITRQ=1 and INITAK=1). This register is writable again as soon as the Initialization Mode is left (INITRQ=0 and INITAK=0).

Read: find the lowest ordered bit set to "1", all other bits will be read as "0"

Write: Anytime when not in Initialization Mode

#### TX2 - TX0 — Transmit Buffer Select

The lowest numbered bit places the respective transmit buffer in the CANTXFG register space (e.g. TX1=1 and TX0=1 selects transmit buffer TX0, TX1=1 and TX0=0 selects transmit buffer TX1)

Read and write accesses to the selected transmit buffer will be blocked, if the corresponding TXEx bit is cleared and the buffer is scheduled for transmission **3.3.1.7 MSCAN Transmitter Flag Register** (CANTFLG).

- 1 = The associated message Buffer is selected, if lowest numbered bit.

- 0 = The associated message buffer is deselected

**NOTE:** The following gives a short programming example of the usage of the CANTBSEL register:

The application software wants to get the next available transmit buffer. It reads the CANTFLG register and writes this value back into the CANTBSEL register. In this example Tx buffers TX1 and TX2 are available. The value read from CANTFLG is therefore 0b0000\_0110. When writing this value back to CANTBSEL the Tx buffer TX1 is selected in the CANTXFG because the lowest numbered bit set to "1" is at bit position 1. Reading back this value out of CANTBSEL results in 0b0000\_0010, because only the lowest numbered bit position set to "1" is presented. This mechanism eases the application software the selection of the next available Tx buffer.

LDD CANTFLG; value read is 0b0000\_0110

STD CANTBSEL; value written is 0b0000\_0110

LDD CANTBSEL; value read is 0b0000\_0010

If all transmit message buffers are deselected no accesses are allowed to the CANTXFG registers.

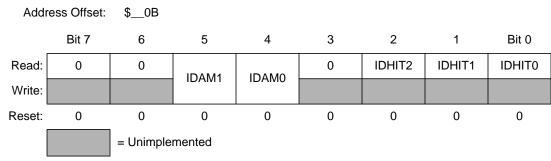

#### 3.3.1.12 MSCAN Identifier Acceptance Control Register (CANIDAC)

The CANIDAC register provides for identifier acceptance control as described below.

Figure 3-12 MSCAN Identifier Acceptance Control Register (CANIDAC)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ=1 and INITAK=1), except bits IDHITx which are read-only

IDAM1 - IDAM0 — Identifier Acceptance Mode

The CPU sets these flags to define the identifier acceptance filter organization **4.3 Identifier Acceptance Filter**. **Table 3-7** summarizes the different settings. In Filter Closed mode, no message is accepted such that the foreground buffer is never reloaded.

**Table 3-7 Identifier Acceptance Mode Settings**

| IDAM1 | IDAM0 | Identifier Acceptance Mode     |

|-------|-------|--------------------------------|

| 0     | 0     | Two 32 bit Acceptance Filters  |

| 0     | 1     | Four 16 bit Acceptance Filters |

| 1     | 0     | Eight 8 bit Acceptance Filters |

| 1     | 1     | Filter Closed                  |

IDHIT2 - IDHIT0 — Identifier Acceptance Hit Indicator

The MSCAN sets these flags to indicate an identifier acceptance hit **4.3 Identifier Acceptance Filter**. **Table 3-8** summarizes the different settings.

| IDHIT2 | IDHIT1 | IDHIT0 | Identifier Acceptance Hit |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | Filter 0 Hit              |

| 0      | 0      | 1      | Filter 1 Hit              |

| 0      | 1      | 0      | Filter 2 Hit              |

| 0      | 1      | 1      | Filter 3 Hit              |

| 1      | 0      | 0      | Filter 4 Hit              |

| 1      | 0      | 1      | Filter 5 Hit              |

| 1      | 1      | 0      | Filter 6 Hit              |

| 1      | 1      | 1      | Filter 7 Hit              |

**Table 3-8 Identifier Acceptance Hit Indication**

The IDHITx indicators are always related to the message in the foreground buffer (RxFG). When a message gets shifted into the foreground buffer of the receiver FIFO the indicators are updated as well.

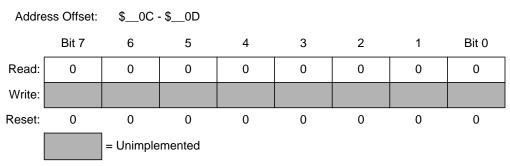

#### 3.3.1.13 Reserved Registers

These registers are reserved for factory testing of the MSCAN module and are not available in normal system operation modes.

Figure 3-13 Reserved Registers

Read: always read \$00 in normal system operation modes

Write: Unimplemented in normal system operation modes

**NOTE:** Writing to these registers when in special modes can alter the MSCAN

functionality.

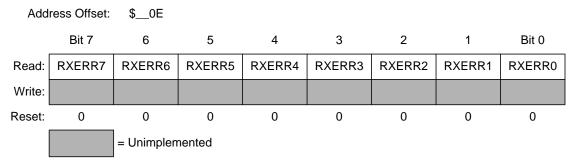

#### 3.3.1.14 MSCAN Receive Error Counter Register (CANRXERR)

This register reflects the status of the MSCAN receive error counter.

Figure 3-14 MSCAN Receive Error Counter Register (CANRXERR)

Read: only when in Sleep Mode (SLPRQ=1 and SLPAK=1) or Initialization Mode (INITRQ=1 and INITAK=1)

Write: Unimplemented

**NOTE:** Reading this register when in any other mode other than Sleep or Initialization

Mode, may return an incorrect value. For MCUs with dual CPUs, this may result

in a CPU fault condition.

**NOTE:** Writing to this register when in special modes can alter the MSCAN functionality.

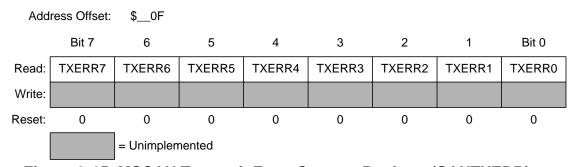

#### 3.3.1.15 MSCAN Transmit Error Counter Register (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Figure 3-15 MSCAN Transmit Error Counter Register (CANTXERR)

Read: only when in Sleep Mode (SLPRQ=1 and SLPAK=1) or Initialization Mode (INITRQ=1 and INITAK=1)

Write: Unimplemented

34 MOTOROLA

**NOTE:** Reading this register when in any other mode other than Sleep or Initialization Mode, may return an incorrect value. For MCUs with dual CPUs, this may result

in a CPU fault condition.

**NOTE:** Writing to this register when in special modes can alter the MSCAN functionality.

#### 3.3.1.16 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

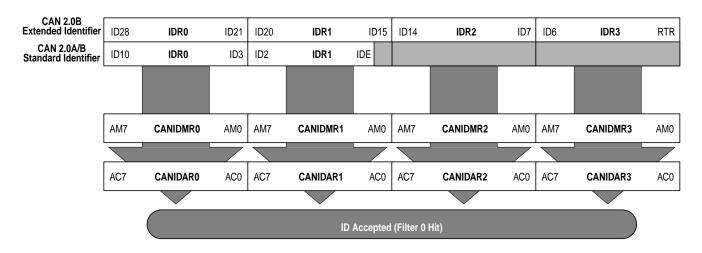

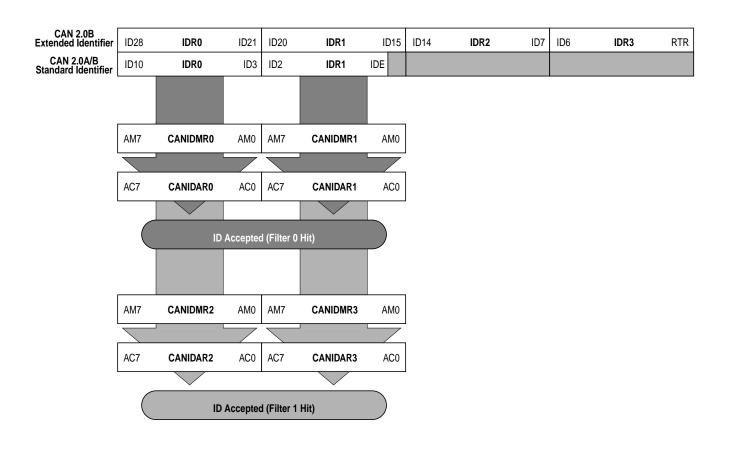

The acceptance registers of the MSCAN are applied on the IDR0 to IDR3 registers **3.3.2.1 Identifier Registers (IDR0-3)** of incoming messages in a bit by bit manner **4.3 Identifier Acceptance Filter**.

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

|                       | Bit 7               | 6        | 5     | 4      | 3        | 2        | 1        | Bit 0         |

|-----------------------|---------------------|----------|-------|--------|----------|----------|----------|---------------|

| А                     | ddress Offset:      | \$10     |       |        |          |          |          | CANIDAR0      |

| Read:<br>Write:       | AC7                 | AC6      | AC5   | AC4    | AC3      | AC2      | AC1      | AC0           |

| Reset:                | 0                   | 0        | 0     | 0      | 0        | 0        | 0        | 0             |

| Ad                    | ddress Offset:      | \$11     |       |        |          |          |          | CANIDAR1      |

| Read:<br>Write:       | AC7                 | AC6      | AC5   | AC4    | AC3      | AC2      | AC1      | AC0           |

| Reset:                | 0                   | 0        | 0     | 0      | 0        | 0        | 0        | 0             |

| Ad                    | ddress Offset:      | \$12     |       |        |          |          |          | CANIDAR2      |

| Read:                 | 4.07                |          | 4.0.5 | 101    |          |          |          |               |

| Write:                | AC7                 | AC6      | AC5   | AC4    | AC3      | AC2      | AC1      | AC0           |

| Write:<br>Reset:      | 0                   | AC6<br>0 | 0     | 0<br>0 | AC3<br>0 | AC2<br>0 | AC1<br>0 | AC0<br>0      |

| Reset:                |                     |          |       |        |          |          |          |               |

| Reset:                | 0                   | 0        |       |        |          |          |          | 0             |

| Reset:<br>Ad<br>Read: | 0<br>ddress Offset: | 0        | 0     | 0      | 0        | 0        | 0        | 0<br>CANIDAR3 |

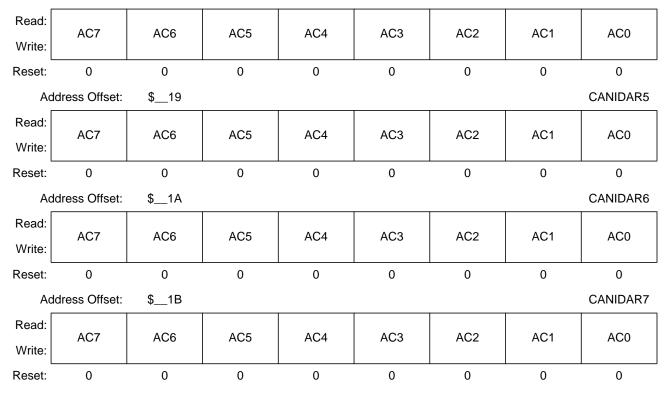

Figure 3-17 MSCAN Identifier Acceptance Registers (2nd Bank)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ=1 and INITAK=1)

AC7 – AC0 — Acceptance Code Bits

AC7 – AC0 comprise a user defined sequence of bits with which the corresponding bits of the related identifier register (IDRn) of the receive message buffer are compared. The result of this comparison is then masked with the corresponding identifier mask register.

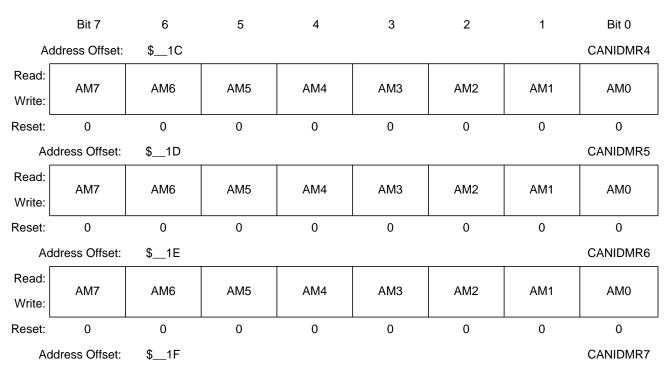

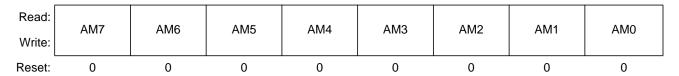

## 3.3.1.17 MSCAN Identifier Mask Registers (CANIDMR0-7)

The identifier mask register specifies which of the corresponding bits in the identifier acceptance register are relevant for acceptance filtering. To receive standard identifiers in 32 bit filter mode, it is required to program the last three bits (AM2 - AM0) in the mask registers CANIDMR1 and CANIDMR5 to "don't care". To receive standard identifiers in 16 bit filter mode, it is required to program the last three bits (AM2 - AM0) in the mask registers CANIDMR1, CANIDMR3, CANIDMR5 and CANIDMR7 to "don't care".

(M) MOTOROLA

| Read:<br>Write: | AM7            | AM6  | AM5 | AM4 | AM3 | AM2 | AM1 | AMO      |

|-----------------|----------------|------|-----|-----|-----|-----|-----|----------|

| Reset:          | 0              | 0    | 0   | 0   | 0   | 0   | 0   | 0        |

| Ac              | ddress Offset: | \$15 |     |     |     |     |     | CANIDMR1 |

| Read:<br>Write: | AM7            | AM6  | AM5 | AM4 | АМ3 | AM2 | AM1 | AM0      |

| Reset:          | 0              | 0    | 0   | 0   | 0   | 0   | 0   | 0        |

| Ac              | ddress Offset: | \$16 |     |     |     |     |     | CANIDMR2 |

| Read:<br>Write: | AM7            | AM6  | AM5 | AM4 | АМЗ | AM2 | AM1 | AMO      |

| Reset:          | 0              | 0    | 0   | 0   | 0   | 0   | 0   | 0        |

| Ac              | ddress Offset: | \$17 |     |     |     |     |     | CANIDMR3 |

| Read:<br>Write: | AM7            | AM6  | AM5 | AM4 | AM3 | AM2 | AM1 | AMO      |

| Reset:          | 0              | 0    | 0   | 0   | 0   | 0   | 0   | 0        |

Figure 3-18 MSCAN Identifier Mask Registers (1st Bank)

Figure 3-19 MSCAN Identifier Mask Registers (2nd Bank)

Figure 3-19 MSCAN Identifier Mask Registers (2nd Bank)

Read: Anytime

Write: Anytime in Initialization Mode (INITRQ=1 and INITAK=1)

AM7 – AM0 — Acceptance Mask Bits

If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.

- 1 = Ignore corresponding acceptance code register bit.

- 0 = Match corresponding acceptance code register and identifier bits.

## 3.3.2 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

For reasons of programmer interface simplification, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

An additional Transmit Buffer Priority Register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers, if the TIME bit is set (3.3.1.1 MSCAN Control 0 Register (CANCTL0)).

The Time Stamp register is written by the MSCAN. The CPU can only read these registers.

| Addr | Register Name                                  |

|------|------------------------------------------------|

| \$x0 | Identifier Register 0                          |

| \$x1 | Identifier Register 1                          |

| \$x2 | Identifier Register 2                          |

| \$x3 | Identifier Register 3                          |

| \$x4 | Data Segment Register 0                        |

| \$x5 | Data Segment Register 1                        |

| \$x6 | Data Segment Register 2                        |

| \$x7 | Data Segment Register 3                        |

| \$x8 | Data Segment Register 4                        |

| \$x9 | Data Segment Register 5                        |

| \$xA | Data Segment Register 6                        |

| \$xB | Data Segment Register 7                        |

| \$xC | Data Length Register                           |

| \$xD | Transmit Buffer Priority Register <sup>1</sup> |

| \$xE | Time Stamp Register (High Byte) <sup>2</sup>   |

| \$xF | Time Stamp Register (Low Byte) <sup>3</sup>    |

**Table 3-9 Message Buffer Organization**

NOTES:

- 1. Not Applicable for Receive Buffers

- 2. Read-Only for CPU

- 3. Read-Only for CPU

**Figure 3-20** shows the common 13 byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in **Figure 3-21**.

All bits of the receive and transmit buffers are 'x' out of reset because of RAM based implementation<sup>1</sup>. All reserved or unused bits of the receive and transmit buffers are always read 'x'.

Figure 3-20 Receive / Transmit Message Buffer Extended Identifier

### NOTES:

1. Exception: The Transmit Priority Registers are "0" out of reset

| Register name | _               | Bit 7 | 6     | 5                 | 4   | 3    | 2    | 1    | Bit 0 | ADDR |

|---------------|-----------------|-------|-------|-------------------|-----|------|------|------|-------|------|

| DSR0          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x4 |

| DSR1          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x5 |

| DSR2          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x6 |

| DSR3          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x7 |

| DSR4          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x8 |

| DSR5          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$x9 |

| DSR6          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$xA |

| DSR7          | Read:<br>Write: | DB7   | DB6   | DB5               | DB4 | DB3  | DB2  | DB1  | DB0   | \$xB |

| DLR           | Read:<br>Write: |       |       |                   |     | DLC3 | DLC2 | DLC1 | DLC0  | \$xC |

|               | [               |       | = Uni | used <sup>1</sup> |     |      |      |      |       | -    |

Figure 3-20 Receive / Transmit Message Buffer Extended Identifier

NOTES:

Read: Anytime for transmit buffers when TXEx flag is set (see 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)) and the corresponding transmit buffer is selected in CANTBSEL (see 3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL)); only when RXF flag is set for receive buffers (see 3.3.1.5 MSCAN Receiver Flag Register (CANRFLG)).

Write: Anytime for transmit buffers when TXEx flag is set (see 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)) and the corresponding transmit buffer is selected in CANTBSEL (see 3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL)); unimplemented for receive buffers

Reset: \$xx because of RAM based implementation

Figure 3-21 Standard Identifier Mapping

<sup>1.</sup> Unused bits are always read 'x'

#### NOTES:

1. Unused bits are always read 'x'

### 3.3.2.1 Identifier Registers (IDR0-3)

The identifier registers for an extended format identifier consist of a total of 32 bits; ID28 - ID0, SRR, IDE, and RTR bits. The identifier registers for a standard format identifier consist of a total of 13 bits; ID10 - ID0, RTR, and IDE bits.

#### ID28 - ID0 — Extended format identifier

The identifiers consist of 29 bits (ID28 - ID0) for the extended format. ID28 is the most significant bit and is transmitted first on the bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.

#### ID10 - ID0 — Standard format identifier

The identifiers consist of 11 bits (ID10 – ID0) for the standard format. ID10 is the most significant bit and is transmitted first on the bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.

### SRR — Substitute Remote Request

This fixed recessive bit is used only in extended format. It must be set to 1 by the user for transmission buffers and is stored as received on the CAN bus for receive buffers.

#### IDE — ID Extended

This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.

- 1 = Extended format (29 bit)

- 0 =Standard format (11 bit)

### RTR — Remote Transmission Request

This flag reflects the status of the Remote Transmission Request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.

- 1 = Remote frame

- 0 = Data frame

### 3.3.2.2 Data Segment Registers (DSR0-7)

The eight data segment registers, each with bits DB7-DB0, contain the data to be transmitted or received. The number of bytes to be transmitted or received is determined by the data length code in the corresponding DLR register.

DB7 - DB0 — Data Bits 7-0

### 3.3.2.3 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

DLC3 - DLC0 — Data Length Code bits

The data length code contains the number of bytes (data byte count) of the respective message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. **Table 3-10** shows the effect of setting the DLC bits.

|      | Data |      |      |               |

|------|------|------|------|---------------|

| DLC3 | DLC2 | DLC1 | DLC0 | byte<br>count |

| 0    | 0    | 0    | 0    | 0             |

| 0    | 0    | 0    | 1    | 1             |

| 0    | 0    | 1    | 0    | 2             |

| 0    | 0    | 1    | 1    | 3             |

| 0    | 1    | 0    | 0    | 4             |

| 0    | 1    | 0    | 1    | 5             |

| 0    | 1    | 1    | 0    | 6             |

| 0    | 1    | 1    | 1    | 7             |

| 1    | 0    | 0    | 0    | 8             |

Table 3-10 Data length codes

### 3.3.2.4 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

• All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (Start of Frame) is sent.

(M) MOTOROLA

• The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Figure 3-22 Transmit Buffer Priority Register (TBPR)

Read: Anytime when TXEx flag is set (see 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)) and the corresponding transmit buffer is selected in CANTBSEL (see 3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL))

Write: Anytime when TXEx flag is set (see 3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)) and the corresponding transmit buffer is selected in CANTBSEL (see 3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL))

### 3.3.2.5 Time Stamp Register (TSRH, TSRL)

If the TIME bit is enabled, the MSCAN will write a special time stamp to the respective registers in the active transmit or receive buffer as soon as a message has been acknowledged on the CAN bus (3.3.1.1 MSCAN Control 0 Register (CANCTL0)). The time stamp is written on the bit sample point for the recessive bit of the ACK delimiter in the CAN frame. In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to "0") during Initialization Mode. The CPU can only read the Time Stamp registers.

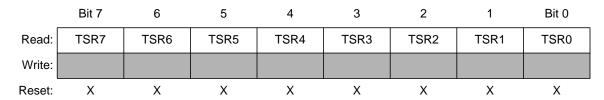

Figure 3-23 Time Stamp Register (TSRH - High Byte)

Address Offset: \$xxxF

Figure 3-24 Time Stamp Register (TSRL - Low Byte)

Read: Anytime when TXEx flag is set (see **3.3.1.7 MSCAN Transmitter Flag Register (CANTFLG)**) and the corresponding transmit buffer is selected in CANTBSEL (see **3.3.1.11 MSCAN Transmit Buffer Selection (CANTBSEL)**)

Write: Unimplemented

# **Section 4 Functional Description**

## 4.1 General

This section provides a complete functional description of the MSCAN. It describes each of the features and modes listed in the introduction.

## 4.2 Message Storage

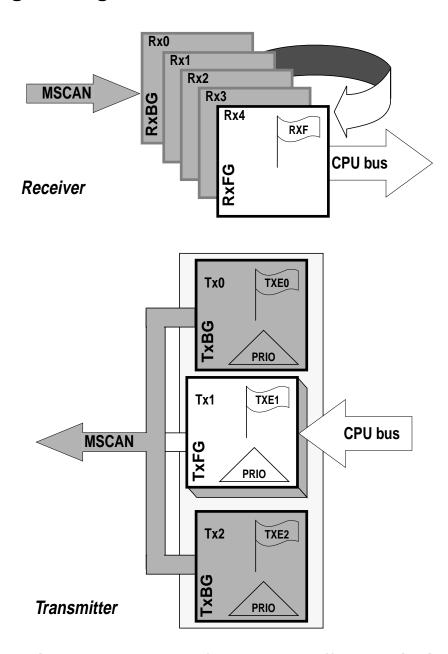

Figure 4-1 User Model for Message Buffer Organization

MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

## 4.2.1 Message Transmit Background

Modern application layer software is built upon two fundamental assumptions:

- Any CAN node is able to send out a stream of scheduled messages without releasing the bus between the two messages. Such nodes arbitrate for the bus immediately after sending the previous message and only release the bus in case of lost arbitration.

- The internal message queue within any CAN node is organized such that the highest priority message is sent out first, if more than one message is ready to be sent.

The above behavior cannot be achieved with a single transmit buffer. That buffer must be reloaded right after the previous message is sent. This loading process lasts a finite amount of time and has to be completed within the Inter-Frame Sequence (IFS)<sup>1</sup> to be able to send an uninterrupted stream of messages. Even if this is feasible for limited CAN bus speeds, it requires that the CPU react with short latencies to the transmit interrupt.

A double buffer scheme de-couples the reloading of the transmit buffer from the actual message sending and, as such, reduces the reactiveness requirements on the CPU. Problems can arise if the sending of a message is finished while the CPU re-loads the second buffer. No buffer would then be ready for transmission and the bus would be released.

At least three transmit buffers are required to meet the first of the above requirements under all circumstances. The MSCAN has three transmit buffers.

The second requirement calls for some sort of internal prioritization which the MSCAN implements with the "local priority" concept described in **4.2.2 Transmit Structures**.

### 4.2.2 Transmit Structures

The MSCAN has a triple transmit buffer scheme which allows multiple messages to be set up in advance and achieve an optimized real-time performance. The three buffers are arranged as shown in **Figure 4-1 User Model for Message Buffer Organization**.

All three buffers have a 13 byte data structure similar to the outline of the receive buffers **3.3.2 Programmer's Model of Message Storage**. An additional **3.3.2.4 Transmit Buffer Priority Register (TBPR)** contains an 8-bit "Local Priority" field (PRIO) (see **3.3.2.4 Transmit Buffer Priority Register (TBPR)**). The remaining two bytes are used for time stamping of a message, if required (see **3.3.2.5 Time Stamp Register (TSRH, TSRL)**).