### 5-V Low Drop Voltage Regulator

#### TLE 7274

#### Features

- Output voltage 5 V ±2%

- Ultra low current consumption: typ. 20μA

- 300 mA current capability

- Very low-drop voltage

- Short-circuit-proof

- Suitable for use in automotive electronics

#### **Functional Description**

The TLE 7274 is a monolithic integrated low-drop voltage regulator for load currents up to 300 mA. An input voltage up to 42 V is regulated to  $V_{Q,nom} = 5.0$  V with a precision of ±2%. The sophisticated design allows to achieve stable operation even with ceramic output capacitors down to 470 nF. The device is designed for the harsh environment of automotive applications. Therefore it is protected against overload, short circuit and over temperature conditions. Of course the TLE 7274 can be used also in all other applications,

where a stabilized 5 V voltage is required. Due to its ultra low stand-by current consumption of typ.  $20\mu$ A the TLE 7274 is dedicated for use in applications permanently connected to  $V_{BAT}$ . An integrated output sink current circuitry keeps the voltage at the Output pin Q below 5.5 V even when reverse currents are applied. Thus connected devices are protected from overvoltage damage.

For applications requiring extremely low noise levels the Infineon voltage regulator family TLE 42XY and TLE 44XY is more suited than the TLE 7274. A mV-range output noise on the TLE 7274 caused by the charge pump operation is unavoidable due to the ultra low quiescent current concept.

| Туре       | Ordering Code | Package                   |

|------------|---------------|---------------------------|

| TLE 7274 D | Q67006-A9728  | P-TO252-3-1, P-TO252-3-11 |

| TLE 7274 G | Q67006-A9731  | P-TO263-3-1               |

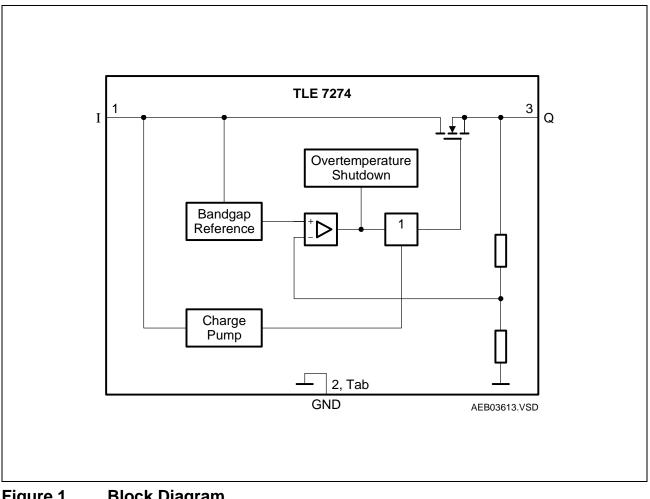

Figure 1 **Block Diagram**

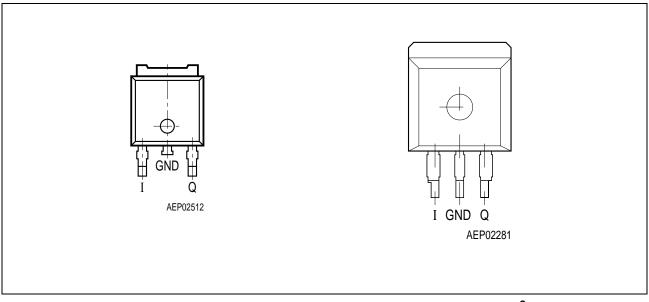

| Figure 2 | Pin Configuration P- | TO252-3 (D-PAK), | P-TO263-3 (D <sup>2</sup> | <sup>2</sup> -PAK)(top view) |

|----------|----------------------|------------------|---------------------------|------------------------------|

|----------|----------------------|------------------|---------------------------|------------------------------|

|         | 1 11 0 |                                                                          |

|---------|--------|--------------------------------------------------------------------------|

| Pin No. | Symbol | Function                                                                 |

| 1       | 1      | Input; block to ground directly at the IC with a ceramic capacitor.      |

| 2       | GND    | Ground; Pin 2 internally connected to heatsink.                          |

| 3       | Q      | <b>Output;</b> block to ground with a ceramic capacitor, $C \ge 470$ nF. |

#### Table 1Pin Definitions and Functions

| Parameter            | Symbol           | Limit Values |      | Unit | Test Condition          |

|----------------------|------------------|--------------|------|------|-------------------------|

|                      |                  | Min.         | Max. |      |                         |

| Input I              |                  |              |      | •    |                         |

| Voltage              | V                | -0.3         | 45   | V    | _                       |

| Current              | I                | -1           | _    | mA   | _                       |

| Output Q             |                  |              |      |      | - <b>-</b>              |

| Voltage              | V <sub>Q</sub>   | -0.3         | 5.5  | V    | -                       |

| Voltage              | VQ               | -0.3         | 6.2  | V    | $t < 10 \text{ s}^{1)}$ |

| Current              | IQ               | -1           | -    | mA   | _                       |

| Temperature          |                  |              | •    | •    | ·                       |

| Junction temperature | T <sub>j</sub>   | -40          | 150  | °C   | -                       |

| Storage temperature  | T <sub>stg</sub> | -50          | 150  | °C   | _                       |

#### Table 2Absolute Maximum Ratings

1) Exposure to these absolute maximum ratings for extended periods (t > 10 s) may affect device reliability.

Note: Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 3Operating Range

| Parameter            | Symbol | Limit Values |      | Limit Values |   | Limit Values Unit |  | Unit | Remarks |

|----------------------|--------|--------------|------|--------------|---|-------------------|--|------|---------|

|                      |        | Min.         | Max. |              |   |                   |  |      |         |

| Input voltage        | VI     | 5.5          | 42   | V            | - |                   |  |      |         |

| Junction temperature | Tj     | -40          | 150  | °C           | - |                   |  |      |         |

Note: In the operating range, the functions given in the circuit description are fulfilled.

#### Table 4Thermal Resistance

| Parameter        | Symbol             | Limit Values |      | Unit | Remarks             |

|------------------|--------------------|--------------|------|------|---------------------|

|                  |                    | Min.         | Max. |      |                     |

| Junction case    | R <sub>thj-c</sub> | _            | 8    | K/W  | _                   |

| Junction ambient | R <sub>thj-a</sub> | _            | 80   | K/W  | TO252 <sup>1)</sup> |

| Junction ambient | R <sub>thj-a</sub> | -            | 55   | K/W  | TO263 <sup>2)</sup> |

1) Worst case, regarding peak temperature; zero airflow; mounted on a PCB FR4,  $80 \times 80 \times 1.5$  mm<sup>3</sup>, heat sink area 300 mm<sup>2</sup>

2) Worst case, regarding peak temperature; zero airflow; mounted on a PCB FR4,  $80 \times 80 \times 1.5$  mm<sup>3</sup>, heat sink area 300 mm<sup>2</sup>

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_a = 25 \degree C$  and the given supply voltage.

#### Table 1 Electrical Characteristics

$V_{\rm I}$  = 13.5 V; – 40 °C <  $T_{\rm j}$  < 150 °C (unless otherwise specified)

| Parameter                                 | Symbol             | Limit Values |      |      | Unit | <b>Measuring Condition</b>                                                 |

|-------------------------------------------|--------------------|--------------|------|------|------|----------------------------------------------------------------------------|

|                                           |                    | Min.         | Тур. | Max. |      |                                                                            |

| Output Q                                  |                    |              | 1    |      |      |                                                                            |

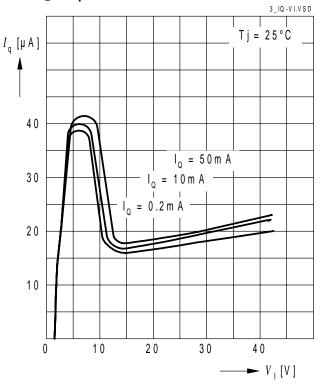

| Output voltage                            | V <sub>Q</sub>     | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < $I_{\rm Q}$ < 300 mA;<br>6 V < $V_{\rm I}$ < 16 V                 |

| Output voltage                            | V <sub>Q</sub>     | 4.9          | 5.0  | 5.1  | V    | 0.1 mA < $I_{\rm Q}$ < 100 mA;<br>6 V < $V_{\rm I}$ < 40 V                 |

| Output current limitation                 | IQ                 | 320          | -    | _    | mA   | 1)                                                                         |

| Output current limitation                 | IQ                 | _            | -    | 800  | mA   | $V_{\rm Q} = 0 \rm V$                                                      |

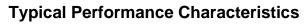

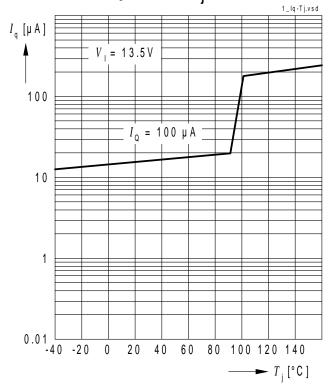

| Current consumption;<br>$I_q = I_1 - I_Q$ | I <sub>q</sub>     | -            | 20   | 25   | μA   | $I_{\rm Q} = 0.1 \text{ mA};$<br>$T_{\rm j} = 25 \text{ °C}$               |

| Current consumption;<br>$I_q = I_1 - I_Q$ | I <sub>q</sub>     | -            | -    | 35   | μA   | $I_{\rm Q}$ = 0.1 mA;<br>$T_{\rm j} \le 80 \ ^{\circ}{\rm C}$              |

| Drop voltage                              | V <sub>dr</sub>    | -            | 250  | 500  | mV   | $I_{\rm Q} = 200 \text{ mA};$<br>$V_{\rm dr} = V_{\rm l} - V_{\rm Q}^{-1}$ |

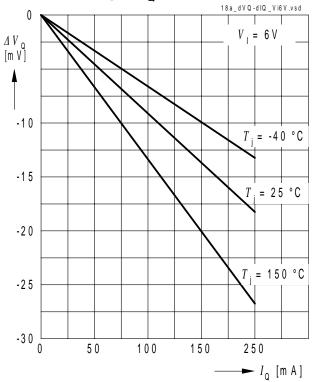

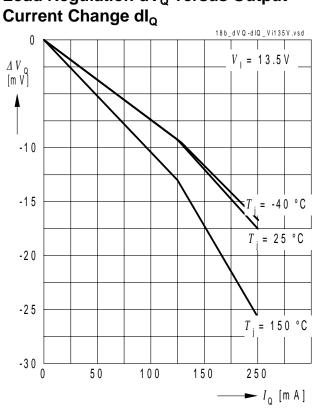

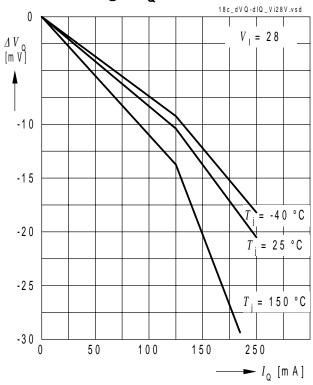

| Load regulation                           | $\Delta V_{Q, lo}$ | -40          | 15   | 40   | mV   | $I_{\rm Q}$ = 5 mA to 250 mA                                               |

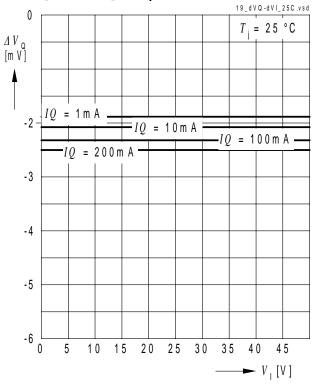

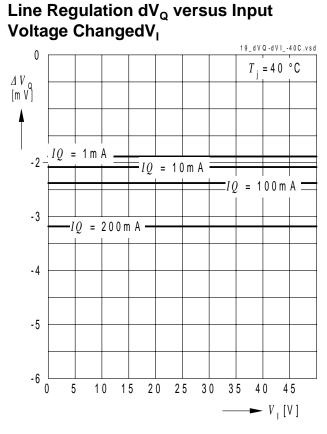

| Line regulation                           | $\Delta V_{Q, li}$ | -20          | 5    | 20   | mV   | $V_{\rm I}$ = 10V to 32 V;<br>$I_{\rm Q}$ = 5 mA                           |

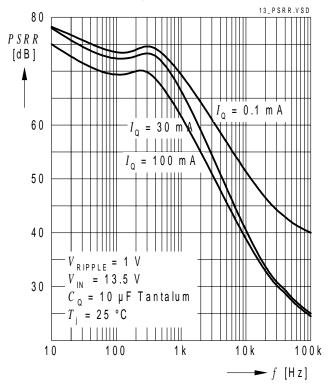

| Power supply ripple rejection             | PSRR               | -            | 60   | -    | dB   | $f_{\rm r}$ = 100 Hz;<br>$V_{\rm r}$ = 0.5 Vpp                             |

| Temperature output voltage drift          | $dV_Q/dT$          | -            | 0.5  | -    | mV/K | _                                                                          |

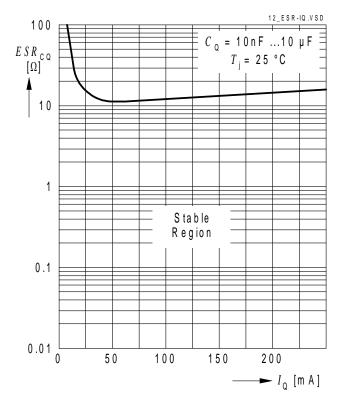

| Output Capacitor                          | CQ                 | 470          | _    | _    | nF   | ESR < 3 Ω                                                                  |

1) Measured when the output voltage  $V_{\rm Q}$  has dropped 100 mV from the nominal value obtained at  $V_{\rm I}$  = 13.5 V.

#### **Application Information**

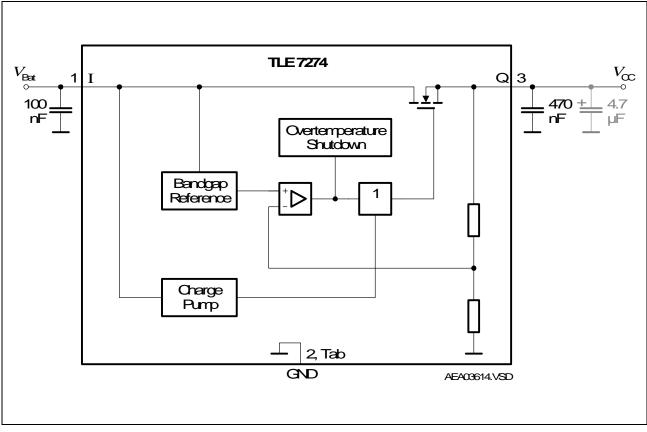

Figure 3 Application Diagram

#### Input, Output

An input capacitor is necessary for damping line influences. A resistor of approx. 1  $\Omega$  in series with  $C_1$ , can damp the LC of the input inductivity and the input capacitor.

In contrast to most low drop voltage regulators the TLE 7274 only needs moderate capacitance at the output to assure stability of the regulation loop. This offers more design flexibility to the circuit designer providing for cost efficient solutions.

The TLE 7274 requires a ceramic output capacitor of at least 470 nF. In order to damp influences resulting from load current surges it is recommended to add an additional electrolytic capacitor of 4.7  $\mu$ F to 47  $\mu$ F at the output as shown in **Figure 3**.

Additionally a buffer capacitor  $C_B$  of > 10 $\mu$ F should be used for the output to suppress influences from load surges to the voltage levels. This one can either be an aluminum electrolytic capacitor or a tantalum capacitor following the application requirements.

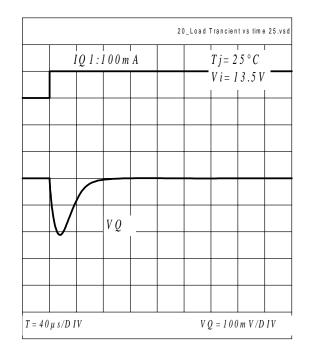

A general recommendation is to keep the drop over the equivalent serial resistor (ESR) together with the discharge of the blocking capacitor below the allowed Headroom of the Application to be supplied (e.g. typ.  $dV_Q = 350$ mV).

Since the regulator output current roughly rises linearly with time the discharge of the capacitor can be calculated as follows:

$dVC_B = dI_Q^* dt/C_B$

The drop across the ESR calculates as:  $dV_{ESR} = dI^*ESR$

To prevent a reset the following relationship must be fullfilled:

$\mathrm{dV_C} + \mathrm{dV_{ESR}} < \mathrm{V_{RH}} = 350 \mathrm{mV}$

Example: Assuming a load current change of  $C_B = 100$ mA, a blocking capacitor of  $dI_Q = 22\mu$ F and a typical regulator reaction time under normal operating conditions of dt ~ 25µs and for special dynamic load conditions, such as load step from very low base load, a reaction time of dt ~ 75µs.

$dV_{C} = dI_{Q}^{*}dt/C_{B} = 100mA * 25\mu s/22\mu F = 113mV$

So for the ESR we can allow

$dV_{ESR} = V_{RH2} - dV_{C} = 350mV - 113mV = 236mV$

The permissible ESR becomes:

$ESR = dV_{ESR} / dI_{Q} = 236 mV / 100 mA = 2.360 hm$

During design-in of the TLE7469 product family, special care needs to be taken with regards to the regulators reaction time to sudden load current changes starting from very low pre-load as well as cyclic load changes. The application note "*TLE7x Voltage Regulators - Application Note about Transient Response at ultra low quiescent current Voltage Regulators*" (see 3\_cip05405.pdf) gives important hints for successful design-in of the Voltage Regulators of the TLE7x family.

#### Current Consumption I<sub>q</sub> versus Junction Temperature T<sub>i</sub>

Înfineon

## Current Consumption $I_q$ versus Output Current $I_{\mbox{\scriptsize Q}}$

### Current Consumption ${\rm I_q}$ versus Input Voltage ${\rm V_l}$

## Output Voltage $V_{Q}$ versus Junction Temperature $T_{i}$

Data Sheet

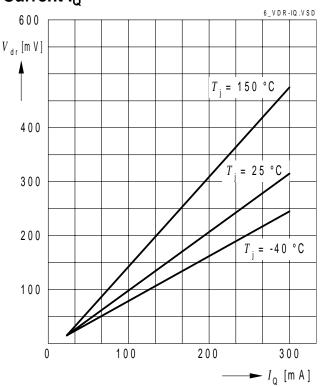

Dropout Voltage  $V_{dr}$  versus Output Current  $I_{\text{Q}}$

### Dropout Voltage $V_{dr}$ versus Junction Temperature $T_i$

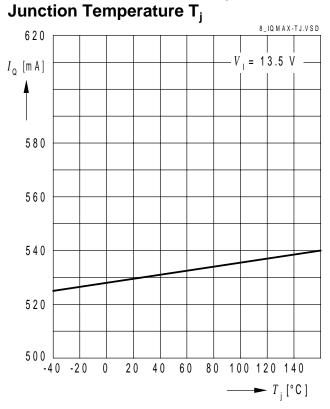

Maximum Output Current I<sub>Q</sub> versus

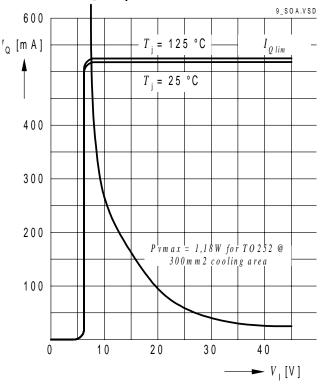

### Maximum Output Current $I_{Q}$ versus Input Voltage V<sub>1</sub>

### **Region of Stability**

### Power Supply Ripple Rejection PSRR versus Frequency f

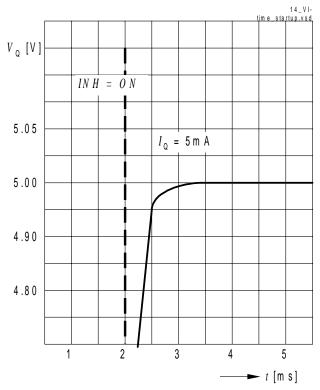

Output Voltage V<sub>Q</sub> Start-up behaviour

Load Regulation  $dV_Q$  versus Output Current Change  $dI_Q$

### Load Regulation dV<sub>Q</sub> versus Output

#### Load Regulation dV<sub>Q</sub> versus Output Current Change dl<sub>o</sub>

Line Regulation dV<sub>Q</sub> versus Input Voltage ChangedV<sub>1</sub>

#### Line Regulation $dV_{\mbox{\scriptsize Q}}$ versus Input Voltage ChangedV<sub>1</sub>

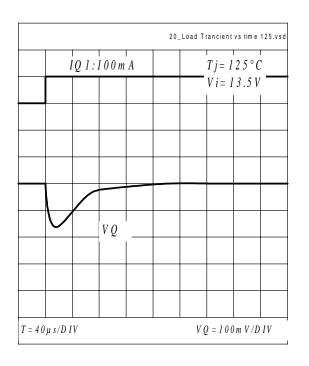

### Load Transient Response Peak Voltage $dV_{\mbox{\scriptsize Q}}$

## Load Transient Response Peak Voltage $dV_{\mbox{\scriptsize Q}}$

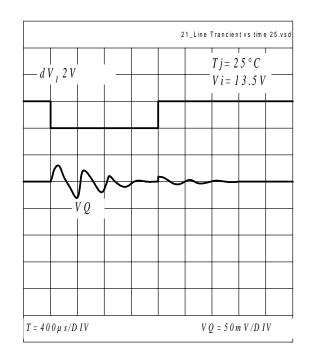

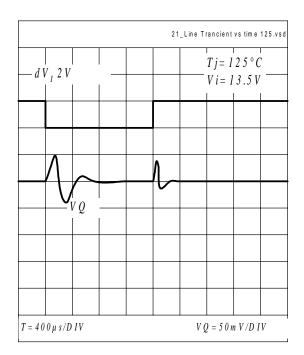

## Line Transient Response Peak Voltage $dV_{\rm Q}$

# Line Transient Response Peak Voltage $\mathsf{dV}_\mathsf{Q}$

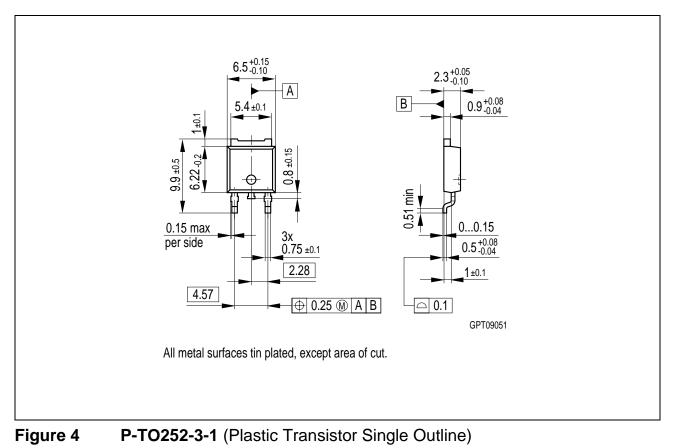

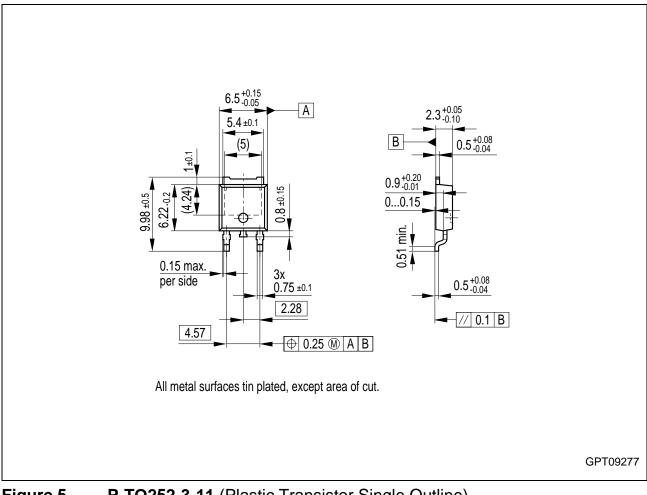

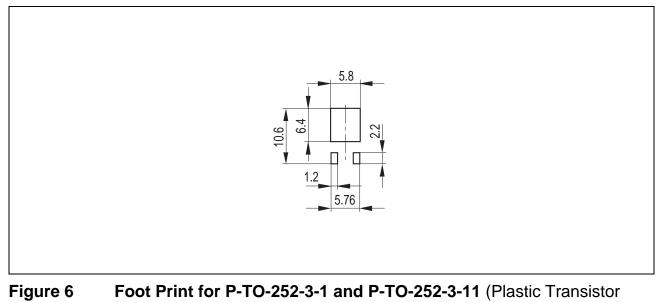

### **Package Outlines**

Figure 5 P-TO252-3-11 (Plastic Transistor Single Outline)

Single Outline)

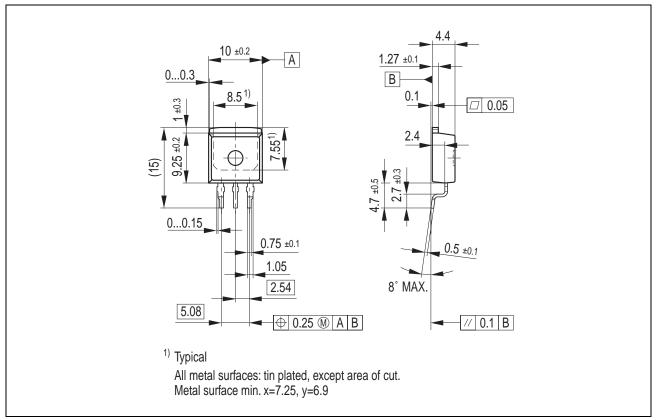

Figure 7 P-TO263-3-1 (Plastic Transistor Single Outline)

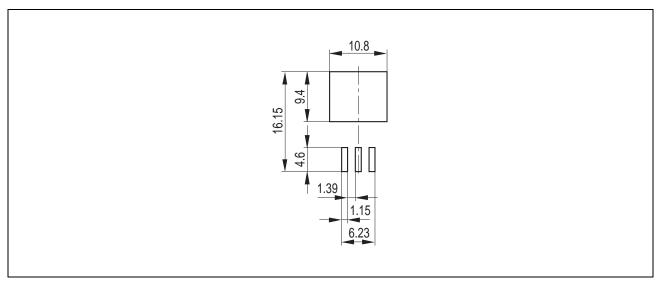

Figure 8 Foot Print for P-TO263-3-1 (Plastic Transistor Single Outline)

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products. Dimensions in mm

#### Remarks

.

Edition 2005-07-30 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2004. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.