### 5-V Low Drop Voltage Regulator

**TLE 4263**

#### **Features**

- Output voltage tolerance ≤ ±2%

- 200 mA output current capability

- Low-drop voltage

- Very low standby current consumption

- Overtemperature protection

- Reverse polarity protection

- Short-circuit proof

- Adjustable reset threshold

- Watchdog

- Wide temperature range

- · Suitable for use in automotive electronics

- Green Product (RoHS compliant)

- AEC Qualified

#### **Functional Description**

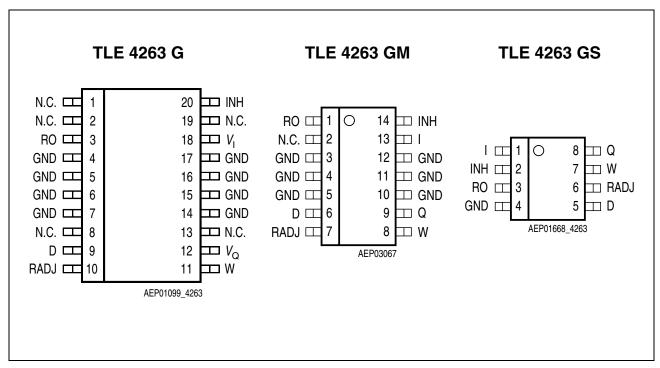

TLE 4263 is a 5-V low drop voltage regulator in a SMD package PG-DSO-14-30, PG-DSO-20-35, or PG-DSO-8-16. The maximum input voltage is 45 V. The maximum output current is more than 200 mA. The IC is short-circuit proof and incorporates temperature protection which turns off the IC at overtemperature.

The IC regulates an input voltage  $V_{\rm I}$  in the range of 6 V <  $V_{\rm I}$  < 45 V to  $V_{\rm Q,nom}$  = 5.0 V. A reset signal is generated for an output voltage of  $V_{\rm Q,rt}$  < 4.5 V. This voltage threshold can be decreased to 3.5 V by external connection of a

voltage divider. The reset delay can be set externally by a capacitor. The integrated watchdog logic supervises the connected microcontroller. The IC can be switched off via the inhibit input, which causes the current consumption to drop from 900  $\mu$ A to typical 0  $\mu$ A.

| Туре        | Package      | Туре        | Package      |

|-------------|--------------|-------------|--------------|

| TLE 4263 GS | PG-DSO-8-16  | TLE 4263 GM | PG-DSO-14-30 |

| TLE 4263 G  | PG-DSO-20-35 |             |              |

Data Sheet 1 Rev. 2.8, 2007-03-20

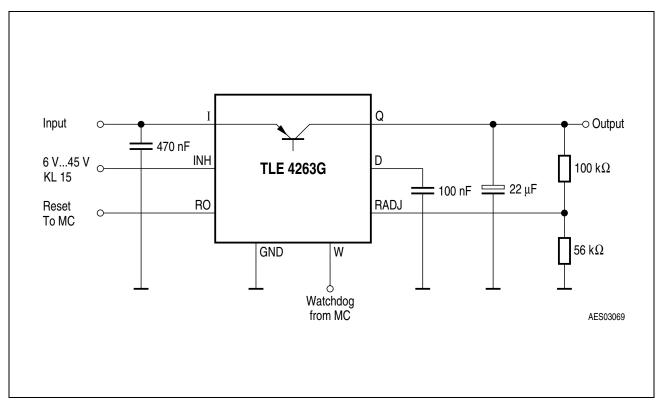

### **Choosing External Components**

The input capacitor  $C_{\rm I}$  is necessary for compensation of line influences. Using a resistor of approx. 1  $\Omega$  in series with  $C_{\rm I}$ , the oscillating circuit consisting of input inductivity and input capacitance can be damped. The output capacitor is necessary for the stability of the regulating circuit. Stability is guaranteed at values  $\geq$  22  $\mu F$  and an ESR of  $\leq$  3  $\Omega$  within the operating temperature range. For small tolerances of the reset delay the spread of the capacitance of the delay capacitor and its temperature coefficient should be noted.

Figure 1 Pin Configuration (top view)

Data Sheet 2 Rev. 2.8, 2007-03-20

| Table 1 | Pin Definitions and Functions |

|---------|-------------------------------|

|---------|-------------------------------|

| Pin<br>PG-DSO-14<br>-30 | Pin<br>PG-DSO-20-<br>35 | Pin<br>PG-DSO-8<br>-16 | Symbol | Function                                                                                                                                                                                      |

|-------------------------|-------------------------|------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | 3                       | 3                      | RO     | Reset output; open-collector output connected to the output via a resistor of 30 k $\Omega$ .                                                                                                 |

| 2                       | 1, 2, 19, 13            | _                      | N.C.   | Not connected                                                                                                                                                                                 |

| 3 - 5, 10 - 12          | 4-7, 14-17              | 4                      | GND    | Ground                                                                                                                                                                                        |

| 6                       | 9                       | 5                      | D      | Reset delay; connected to ground with a capacitor.                                                                                                                                            |

| 7                       | 10                      | 6                      | RADJ   | Reset threshold; to adjust the switching threshold connect a voltage divider (output to GND) to the pin. If this input is connected to GND, reset is triggered at an output voltage of 4.5 V. |

| 8                       | 11                      | 7                      | W      | Watchdog; rising edge triggered input for monitoring a microcontroller.                                                                                                                       |

| 9                       | 12                      | 8                      | Q      | <b>5-V output voltage</b> ; block to ground with a capacitor, $C \ge 22 \mu F$ , ESR $\le 3 \Omega$ at 10 kHz                                                                                 |

| 13                      | 18                      | 1                      | I      | Input voltage; block to ground directly at the IC with a ceramic capacitor.                                                                                                                   |

| 14                      | 20                      | 2                      | INH    | Inhibit; TTL-compatible, low-active input.                                                                                                                                                    |

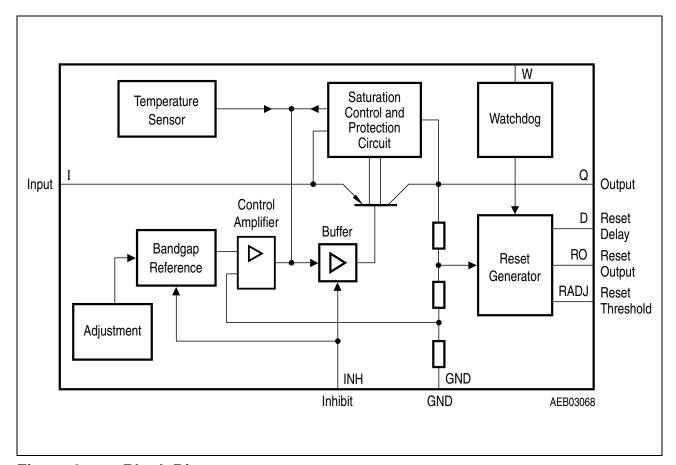

### **Circuit Description**

The control amplifier compares a reference voltage, which is kept highly accurate by resistance adjustment, to a voltage that is proportional to the output voltage and drives the base of the series transistor via a buffer. Saturation control as a function of the load current prevents any over-saturation of the power element. If the externally scaled down output voltage at the reset threshold input drops below 1.35 V, the external reset delay capacitor is discharged by the reset generator. When the voltage of the capacitor reaches the lower threshold  $V_{\rm DRL}$ , a reset signal occurs at the reset output and is held until the upper threshold  $V_{\rm DU}$  is exceeded. If the reset threshold input is connected to GND, reset is triggered at an output voltage of typ. 4.65 V. A connected microcontroller will be monitored through the watchdog logic. In case of missing pulses at pin W, the reset output is set to low. The pulse sequence time can be set in a wide range with the reset delay capacitor. The IC can be switched at the TTL-compatible, low-active inhibit input. The IC also incorporates a number of internal circuits for protection against:

- Overload

- Overtemperature

- Reverse polarity

Figure 2 Block Diagram

Data Sheet 4 Rev. 2.8, 2007-03-20

Table 2 Absolute Maximum Ratings

| Parameter            | Symbol      | Lim  | it Values | Unit | Remarks            |  |

|----------------------|-------------|------|-----------|------|--------------------|--|

|                      |             | Min. | Min. Max. |      |                    |  |

| Input I              |             |      |           | •    |                    |  |

| Input voltage        | $V_{I}$     | -42  | 45        | V    | _                  |  |

| Input current        | $I_{I}$     | _    | _         | _    | internally limited |  |

| Reset Output RO      |             |      |           |      |                    |  |

| Voltage              | $V_{R}$     | -0.3 | 42        | V    | _                  |  |

| Current              | $I_{R}$     | _    |           | _    | internally limited |  |

| Reset Threshold RADJ |             |      |           |      |                    |  |

| Voltage              | $V_{RADJ}$  | -0.3 | 6         | V    | _                  |  |

| Reset Delay D        |             |      |           |      |                    |  |

| Voltage              | $V_{D}$     | -0.3 | 42        | V    | _                  |  |

| Current              | $I_{D}$     | _    |           |      | internally limited |  |

| Output Q             |             |      |           |      |                    |  |

| Voltage              | $V_{Q}$     | -0.3 | 7         | ٧    | _                  |  |

| Current              | $I_{Q}$     | _    | _         |      | internally limited |  |

| Inhibit INH          |             |      |           |      |                    |  |

| Voltage              | $V_{INH}$   | -42  | 45        | V    | _                  |  |

| Watchdog W           |             |      |           |      |                    |  |

| Voltage              | $V_{W}$     | -0.3 | 6         | ٧    | _                  |  |

| Ground GND           |             |      |           | •    |                    |  |

| Current              | $I_{GND}$   | -0.5 | _         | Α    | _                  |  |

| Temperature          |             |      |           | •    |                    |  |

| Junction temperature | $T_{\rm j}$ | _    | 150       | °C   | _                  |  |

| Storage temperature  | $T_{stg}$   | -50  | 150       | °C   | _                  |  |

| Operating Range      |             | _    |           |      |                    |  |

| Input voltage        | $V_{l}$     | _    | 45        | V    | _                  |  |

| Junction temperature | $T_{\rm j}$ | -40  | 150       | °C   | _                  |  |

|                      | <u> </u>    | _1   | •         | E    | 1                  |  |

Table 2

Absolute Maximum Ratings (cont'd)

| Parameter          | Symbol             | Lim       | it Values | Unit | Remarks                                                       |  |  |  |

|--------------------|--------------------|-----------|-----------|------|---------------------------------------------------------------|--|--|--|

|                    |                    | Min. Max. |           |      |                                                               |  |  |  |

| Thermal Resistance |                    |           |           |      |                                                               |  |  |  |

| Junction-ambient   | $R_{\text{thj-a}}$ | _         | 112       | K/W  | PG-DSO-14-30 <sup>1)</sup> ;<br>Footprint only                |  |  |  |

|                    |                    | _         | 92        | K/W  | PG-DSO-14-30 <sup>1)</sup> ;<br>300 mm <sup>2</sup> Heat sink |  |  |  |

|                    |                    | _         | 185       | K/W  | PG-DSO-8-16 <sup>1)</sup> ;<br>Footprint only                 |  |  |  |

|                    |                    | -         | 164       | K/W  | PG-DSO-8-16 <sup>1)</sup> ;<br>300 mm <sup>2</sup> Heat sink  |  |  |  |

| Junction-pin       | $R_{thj-p}$        | _         | 32        | K/W  | PG-DSO-14-30 <sup>2)</sup>                                    |  |  |  |

<sup>1)</sup> Worst case; package mounted on PCB  $80 \times 80 \times 1.5 \text{ mm}^3$ ;  $35\mu$  Cu;  $5\mu$  Sn; zero airflow.

<sup>2)</sup> Measured to pin 4.

Table 3

Characteristics

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm j}$  < 125 °C;  $V_{\rm INH}$  > 3.5 V; (unless specified otherwise)

| Parameter                              | Symbol                                                      | Limit Values |                 |                  | Unit           | Test Condition                                                                                                    |  |

|----------------------------------------|-------------------------------------------------------------|--------------|-----------------|------------------|----------------|-------------------------------------------------------------------------------------------------------------------|--|

|                                        |                                                             | Min.         | Тур.            | Max.             |                |                                                                                                                   |  |

| Normal Operation                       |                                                             | 1            | <b>-</b>        | <b>-1</b>        | •              |                                                                                                                   |  |

| Output voltage                         | $V_{Q}$                                                     | 4.90         | 5.00            | 5.10             | V              | 5 mA $\leq I_{Q} \leq$ 150 mA;<br>6 V $\leq V_{I} \leq$ 28 V                                                      |  |

| Output voltage                         | $V_{Q}$                                                     | 4.90         | 5.00            | 5.10             | V              | $6 \text{ V} \le V_{\text{I}} \le 32 \text{ V};$ $I_{\text{Q}} = 100 \text{ mA};$ $T_{\text{j}} = 100 \text{ °C}$ |  |

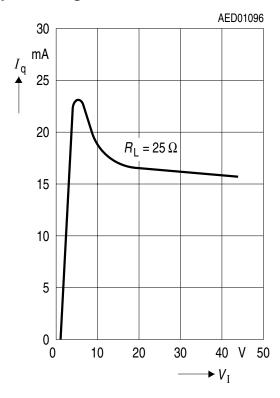

| Output current                         | $I_{Q}$                                                     | 200          | 250             | 400              | mA             | 1)                                                                                                                |  |

| Current consumption; $I_q = I_l - I_Q$ | $I_{q}$                                                     | _            | 0               | 50               | μΑ             | $V_{INH} = 0$                                                                                                     |  |

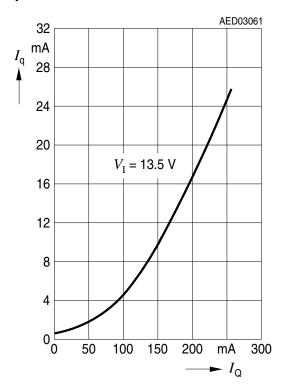

| •                                      | $egin{array}{c} I_{q} & & & & & & & & & & & & & & & & & & $ | _<br>_<br>_  | 900<br>10<br>15 | 1300<br>18<br>23 | μA<br>mA<br>mA | $I_{\rm Q}$ = 0 mA<br>$I_{\rm Q}$ = 150 mA<br>$I_{\rm O}$ = 150 mA; $V_{\rm I}$ = 4.5 V                           |  |

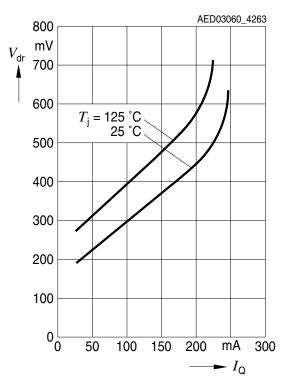

| Drop voltage                           | $V_{dr}$                                                    | _            | 0.35            | 0.50             | V              | $I_{\rm Q}$ = 150 mA <sup>1)</sup>                                                                                |  |

| Load regulation                        | $\Delta V_{Q,lo}$                                           | _            | _               | 25               | mV             | $I_{\rm Q}$ = 5 mA to 150 mA                                                                                      |  |

| Line regulation                        | $\Delta V_{Q.li}$                                           | _            | 3               | 25               | mV             | $V_{\rm I}$ = 6 V to 28 V;<br>$I_{\rm Q}$ = 150 mA                                                                |  |

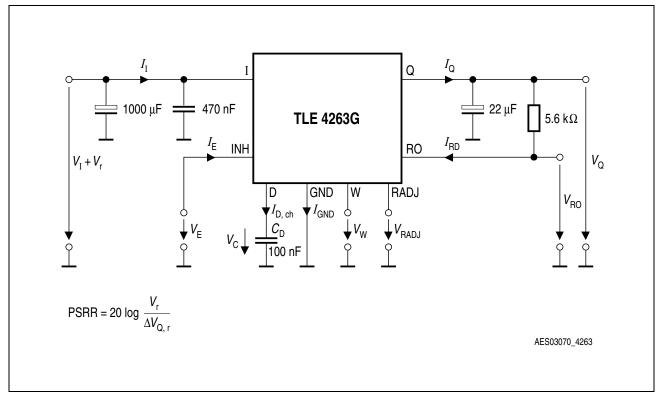

| Power Supply Ripple<br>Rejection       | PSRR                                                        | _            | 54              | _                | dB             | $f_{\rm r}$ = 100 Hz;<br>$V_{\rm r}$ = 0.5 Vpp                                                                    |  |

| Reset Generator                        |                                                             | •            | •               | 1                | •              |                                                                                                                   |  |

| Switching threshold                    | $V_{Q,rt}$                                                  | 4.5          | 4.65            | 4.8              | V              | $V_{RADJ}$ = 0 V                                                                                                  |  |

| Reset adjust threshold                 | $V_{RADJ,th}$                                               | 1.26         | 1.35            | 1.44             | V              | V <sub>Q</sub> > 3.5 V                                                                                            |  |

| Reset low voltage                      | $V_{RO,I}$                                                  | _            | 0.10            | 0.40             | V              | $I_{\rm RO}$ = 1 mA                                                                                               |  |

| Saturation voltage                     | $V_{D,sat}$                                                 | _            | 50              | 100              | mV             | $V_{\rm Q} < V_{\rm R,th}$                                                                                        |  |

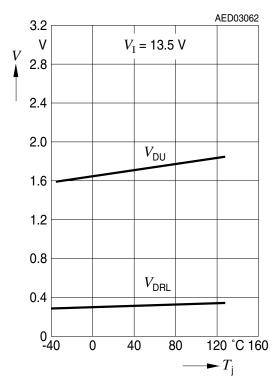

| Upper timing threshold                 | $V_{DU}$                                                    | 1.45         | 1.70            | 2.05             | V              | _                                                                                                                 |  |

| Lower reset timing threshold           | $V_{DRL}$                                                   | 0.20         | 0.35            | 0.55             | V              | _                                                                                                                 |  |

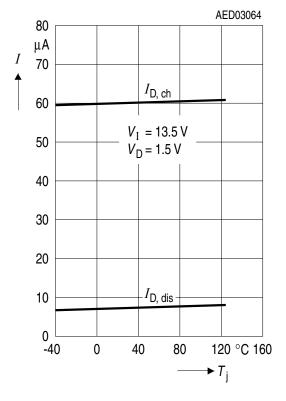

| Charge current                         | $I_{D,ch}$                                                  | 40           | 60              | 85               | μΑ             | _                                                                                                                 |  |

| Reset delay time                       | $t_{\rm rd}$                                                | 1.3          | 2.8             | 4.1              | ms             | $C_{\rm D}$ = 100 nF                                                                                              |  |

| Reset reaction time                    | $t_{\rm rr}$                                                | 0.5          | 1.2             | 4                | μs             | $C_{\rm D} = 100 \; {\rm nF}$                                                                                     |  |

### Table 3 Characteristics (cont'd)

$V_{\rm I}$  = 13.5 V; -40 °C <  $T_{\rm j}$  < 125 °C;  $V_{\rm INH}$  > 3.5 V; (unless specified otherwise)

| Parameter              | Symbol Limit Values |      | ues  | Unit | <b>Test Condition</b> |                               |  |

|------------------------|---------------------|------|------|------|-----------------------|-------------------------------|--|

|                        |                     | Min. | Тур. | Max. |                       |                               |  |

| Watchdog               |                     |      |      |      |                       |                               |  |

| Discharge current      | $I_{D,wd}$          | 4.40 | 6.25 | 9.10 | μΑ                    | $V_{\rm D}$ = 1.0 V           |  |

| Upper timing threshold | $V_{DU}$            | 1.45 | 1.70 | 2.05 | V                     | -                             |  |

| Lower timing threshold | $V_{DWL}$           | 0.20 | 0.35 | 0.55 | V                     | _                             |  |

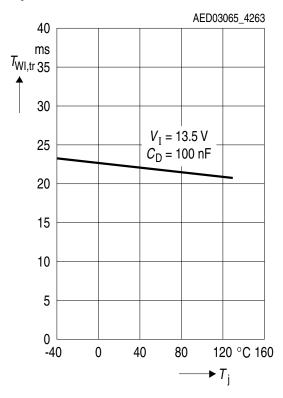

| Watchdog trigger time  | $T_{WI,tr}$         | 16   | 22.5 | 27   | ms                    | $C_{\rm D} = 100 \; {\rm nF}$ |  |

| Inhibit                |                     |      |      |      |                       |                               |  |

| Switching voltage      | $V_{INH,ON}$        | 3.6  | _    | _    | V                     | IC turned on                  |  |

| Turn-OFF voltage       | $V_{INH,OFF}$       | _    | _    | 0.8  | V                     | IC turned off                 |  |

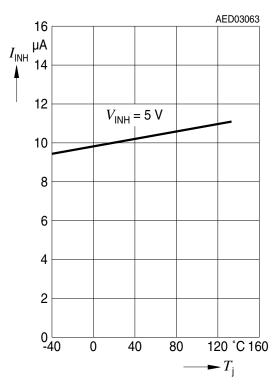

| Input current          | $I_{INH}$           | 5    | 10   | 25   | μΑ                    | $V_{INH} = 5 \; V$            |  |

<sup>1)</sup> Drop voltage =  $V_{\rm i}$  -  $V_{\rm Q}$  (measured when the output voltage has dropped 100 mV from the nominal value obtained at 6 V input).

Note: The reset output is low within the range  $V_{\rm Q}$  = 1 V to  $V_{\rm Q,rt}$ .

Data Sheet 8 Rev. 2.8, 2007-03-20

Figure 3 Application Circuit

Figure 4 Test Circuit

Data Sheet 9 Rev. 2.8, 2007-03-20

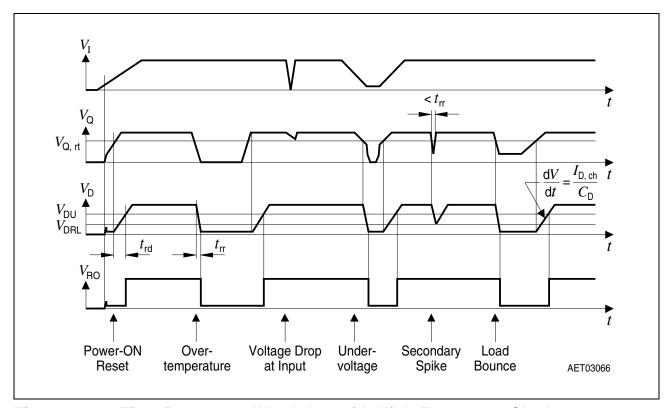

### **Reset Timing**

The power-on reset delay time is defined by the charging time of an external capacitor  $C_{\rm D}$  which can be calculated as follows:

$$C_{\rm D} = (t_{\rm rd} \times I_{\rm D.ch})/\Delta V \tag{1}$$

#### **Definitions:**

- $C_D$  = delay capacitor

- $t_{rd}$  = reset delay time

- $I_{D,ch}$  = charge current, typical 60  $\mu$ A

- $\Delta \dot{V} = V_{DU}$ , typical 1.70 V

- $V_{DU}$  = upper delay switching threshold at  $C_D$  for reset delay time

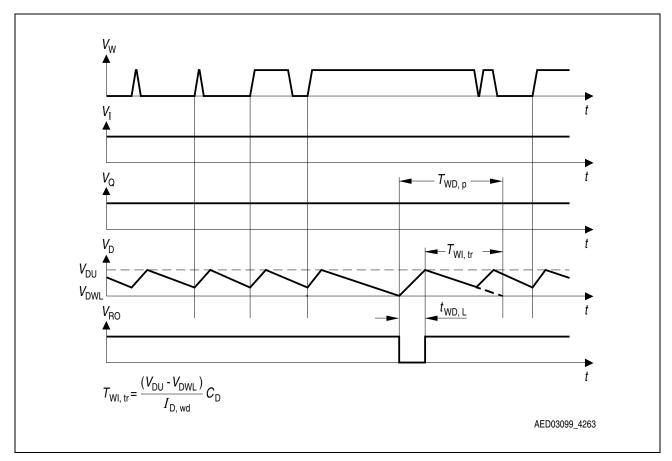

Figure 5 Time Response, Watchdog with High-Frequency Clock

Data Sheet 10 Rev. 2.8, 2007-03-20

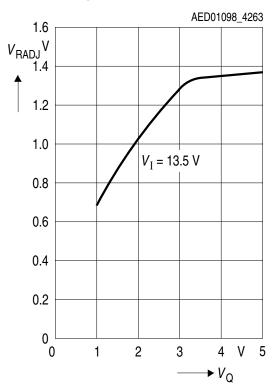

### **Reset Switching Threshold**

The present default value is typ. 4.65 V. When using the TLE 4263 the reset threshold can be set to 3.5 V <  $V_{\rm Q,rt}$  < 4.6 V by connecting an external voltage divider to pin RADJ. The calculation can be easily done since the reset adjust input current can be neglected. If this feature is not needed, the pin has to be connected to GND.

$$V_{\text{O.rt}} = (1 + R_1/R_2) \times V_{\text{BADJ.th}} \tag{2}$$

#### **Definitions:**

- $V_{O,rt}$  = reset threshold

- V<sub>RADJ.th</sub> = comparator reference voltage, typical 1.35 V

### **Watchdog Timing**

The frequency of the watchdog pulses has to be higher than the minimum pulse sequence which is set by the external reset delay capacitor  $C_{\rm D}$ . Calculation can be done according to the formula given in **Figure 6**.

Figure 6 Timing of the Watchdog Function Reset

Data Sheet 11 Rev. 2.8, 2007-03-20

### Reset Switching Threshold versus Output Voltage

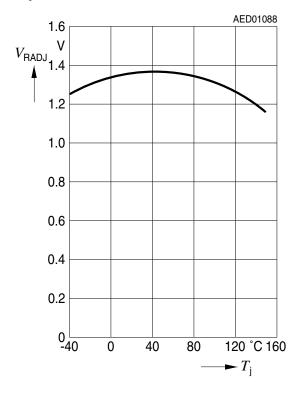

## Reset Switching Threshold versus Temperature

# Timing Threshold Voltage $V_{\rm DU}$ and $V_{\rm DRL}$ versus Temperature

# **Current Consumption of Inhibit versus Temperature**

## Drop Voltage versus Output Current

## **Current Consumption versus Output Current**

## **Current Consumption versus Input Voltage**

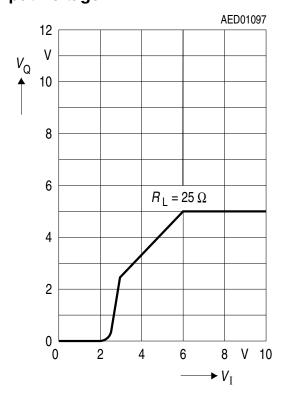

# Output Voltage versus Input Voltage

# **Charge Current and Discharge Current versus Temperature**

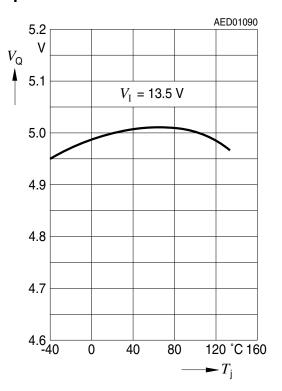

## Output Voltage versus Temperature

### Pulse Time versus Temperature

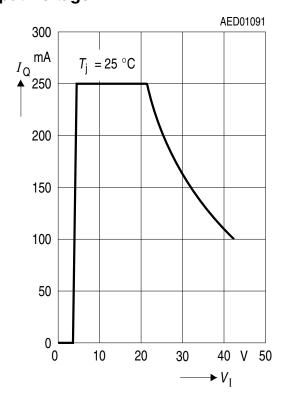

# Output Current versus Input Voltage

### **Package Outlines**

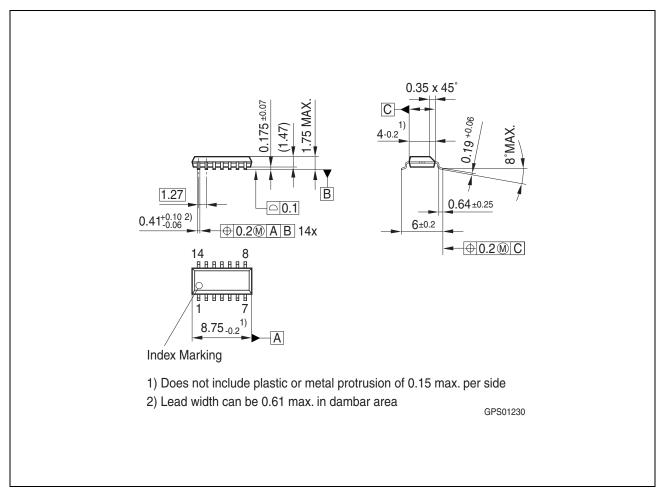

Figure 7 PG-DSO-14-30 (Plastic Dual Small Outline)

### **Green Product** (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm

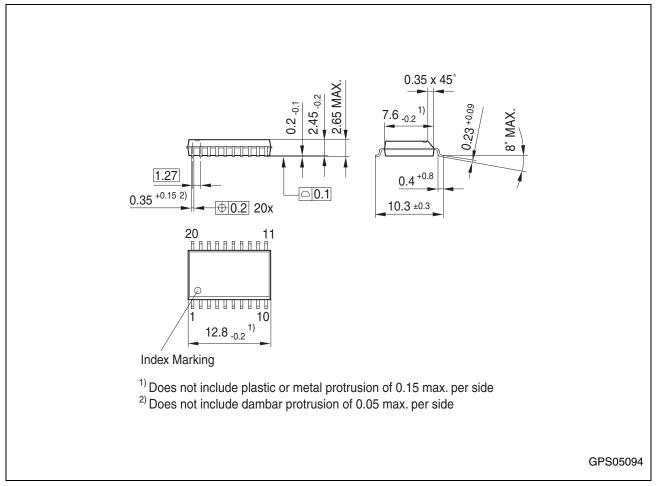

Figure 8 PG-DSO-20-35 (Plastic Dual Small Outline)

### **Green Product** (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm

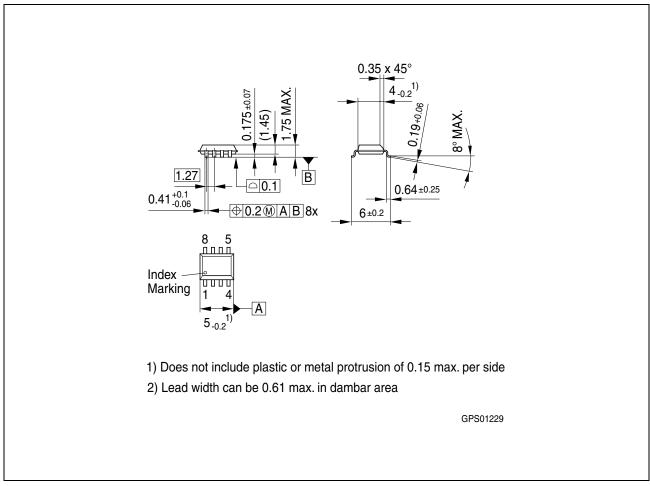

Figure 9 PG-DSO-8-16 (Plastic Dual Small Outline)

#### **Green Product** (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products.

SMD = Surface Mounted Device

Dimensions in mm

### **Revision History**

| Version  | Date       | Changes                                                                                                                                                                                                                                                                      |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 2.8 | 2007-03-20 | Initial version of RoHS-compliant derivate of TLE 4263  Page 1: AEC certified statement added  Page 1 and Page 15 ff:RoHS compliance statement and  Green product feature added  Page 1 and Page 15 ff: Package changed to RoHS  compliant version  Legal Disclaimer updated |

Edition 2007-03-20

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2007 Infineon Technologies AG

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.